Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 101

6-8

MAXQ610 User’s Guide

Each bit in this register is set when a negative edge or a positive edge (depending on the ITn bit setting) is detected

on the corresponding interrupt pin . Once an external interrupt has been detected, the interrupt flag bit remains set until

cleared by software or a reset . Setting any of these bits causes the corresponding interrupt to trigger if it is enabled

to do so .

Bit 7: External Interrupt 15 Edge Detect (IE15)

Bit 6: External Interrupt 14 Edge Detect (IE14)

Bit 5: External Interrupt 13 Edge Detect (IE13)

Bit 4: External Interrupt 12 Edge Detect (IE12)

Bit 3: External Interrupt 11 Edge Detect (IE11)

Bit 2: External Interrupt 10 Edge Detect (IE10)

Bit 1: External Interrupt 9 Edge Detect (IE9)

Bit 0: External Interrupt 8 Edge Detect (IE8)

Each bit in this register controls the enable for one external interrupt . If a bit is set to 1, the corresponding interrupt is

enabled (if it is not otherwise masked) . If a bit is set to 0, its corresponding interrupt is disabled .

Bit 7: External Interrupt 7 Enable (EX7)

Bit 6: External Interrupt 6 Enable (EX6)

Bit 5: External Interrupt 5 Enable (EX5)

Bit 4: External Interrupt 4 Enable (EX4)

Bit 3: External Interrupt 3 Enable (EX3)

Bit 2: External Interrupt 2 Enable (EX2)

Bit 1: External Interrupt 1 Enable (EX1)

Bit 0: External Interrupt 0 Enable (EX0)

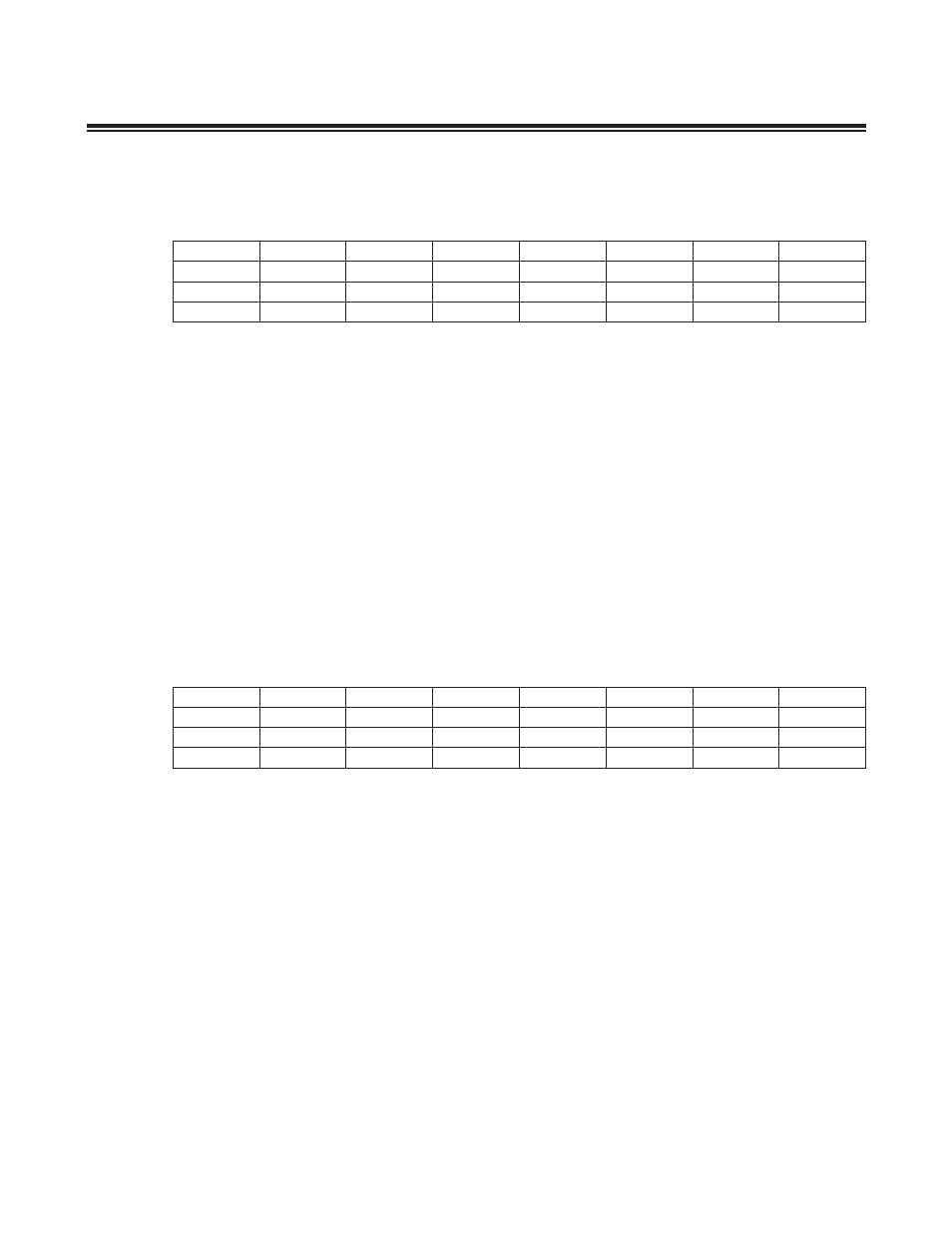

Register Name

EIF1

Register Description

External Interrupt Flag 1 Register

Register Address

M0[07h]

Register Name

EIE0

Register Description

External Interrupt Enable 0 Register

Register Address

M0[08h]

Bit #

7

6

5

4

3

2

1

0

Name

IE15

IE14

IE13

IE12

IE11

IE10

IE9

IE8

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw

Bit #

7

6

5

4

3

2

1

0

Name

EX7

EX6

EX5

EX4

EX3

EX2

EX1

EX0

Reset

0

0

0

0

0

0

0

0

Access

rw

rw

rw

rw

rw

rw

rw

rw