4 interrupt prioritization by software, 2 .9 .4 interrupt prioritization by software -26, Table 2-7 . interrupt priority -26 – Maxim Integrated MAXQ610 User Manual

Page 30: Maxq610 user’s guide, Table 2-7. interrupt priority

2-26

MAXQ610 User’s Guide

External interrupts, when enabled, can be used as switchback sources from power-management mode . There is no

latency associated with the switchback because the circuit is being clocked by an undivided clock source vs . the

divide-by-256 system clock . For the same reason, there is no latency for other switchback sources that do not qualify

as interrupt sources .

2.9.4 Interrupt Prioritization by Software

There are three levels of interrupt priorities: level 0 to 2 . Level 0 is the highest priority and level 2 is the lowest . All

interrupts have individual priority bits in the IPR0 register to allow each interrupt to be assigned a priority level . All inter-

rupts have a natural priority or hierarchy . In this manner, when a set of interrupts has been assigned the same prior-

ity, this natural priority hierarchy determines which interrupt is allowed to take precedence if multiple interrupts occur

simultaneously . The natural hierarchy is determined by analyzing potential interrupts in a sequential manner with the

preferred order as listed in Table 2-7 . Once an interrupt is being processed, only an interrupt with higher priority level

can preempt it . Therefore, the MAXQ610 supports a maximum of two levels of interrupt nesting .

For example, suppose three interrupts occur simultaneously and the assigned priorities (IPV bits) for each of the inter-

rupt sources are as follows:

• IR Timer: assigned priority level 1

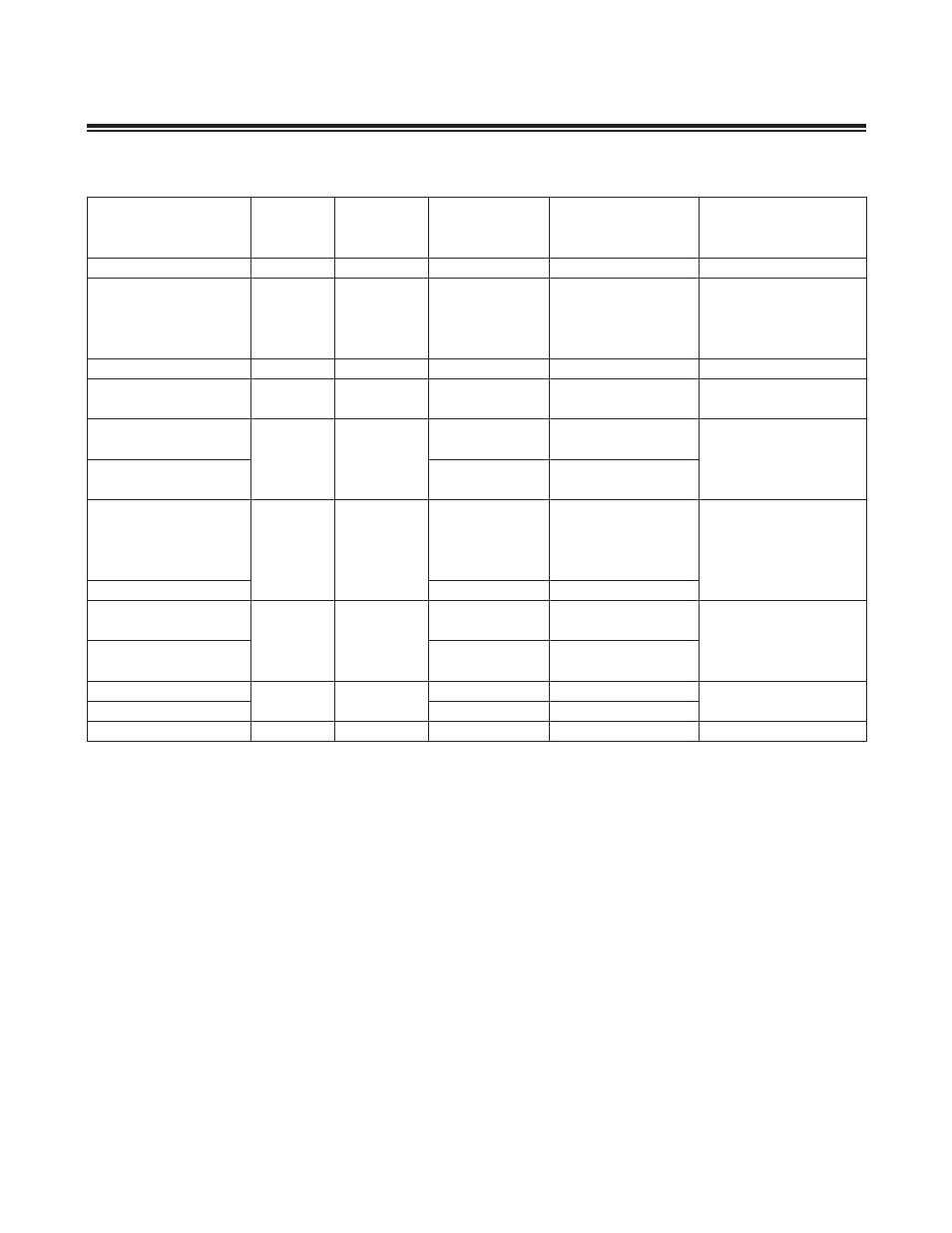

Table 2-7. Interrupt Priority

*With the exception of the power-fail interrupt, all interrupts require that the IGE bit be set to 1 to generate an interrupt request,

regardless of the individual interrupt enable listed. The power-fail interrupt is not governed by IGE (i.e., interrupt request genera-

tion is controlled solely by the PFIE enable bit).

INTERRUPT

VECTOR

ADDRESS

(hex)

NATURAL

PRIORITY

FLAG

ENABLE*

PRIORITY CONTROL

Power Fail

20h

0

PFI (PWCN .2)

PFIE (PWCN .1)

IPV0[1:0] (IPR0[1:0])

Memory Fault

28h

1

PULRF (IC .4),

PULWF (IC .5),

PSYRF (IC .6),

PSYWF (IC .7)

MPE (SC .10)

IPV1[1:0] (IPR0[3:2])

External INT[7:0]

30h

2

IE[7:0] (EIF0)

EX[7:0] (EIE0)

IPV2[1:0] (IPR0[5:4])

IR Timer

38h

3

IROV (IRCNB .0),

IRIF (IRCNB .1)

IRIE (IRCNB .2)

IPV3[1:0] (IPR0[7:6])

Serial Port 0

40h

4

RI (SCON0 .0),

TI (SCON0 .1)

ESI (SMD0 .2)

IPV4[1:0] (IPR0[9:8])

Serial Port 1

RI (SCON1 .0),

TI (SCON1 .1)

ESI (SMD1 .2)

SPI

48h

5

MODF (SPICN .3),

WCOL (SPICN .4),

ROVR (SPICN .5),

SPIC (SPICN .6)

ESPII (SPICF .7)

IPV5[1:0] (IPR0[11:10])

External INT[15:8]

IE[15:8] (EIF1)

EX15[7:8] (EIE1)

Timer B0

50h

6

TFB (TBOCN .7),

EXFB (TB0CN .6)

ETB (TB0CN .1)

IPV6[1:0] (IPR0[13:12])

Timer B1

TFB (TB1CN .7),

EXFB (TB1CN .6)

ETB (TB1CN .1)

Wake-Up Timer

58h

7

WTF (WUTC .1)

WTE (WUTC .0)

IPV7[1:0] (IPR0[15:14])

Watchdog Timer

WDIF (WDCN .3)

EWDI (WDCN .6)

Unhandled Interrupt

98h

8

None

None

None