Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 71

4-16

MAXQ610 User’s Guide

REGISTER

DESCRIPTION

DPC, 0Eh[04h]

Data Pointer Control Register (16 bits)

Initialization

This register is cleared to 005Ch on all forms of reset .

Access

Unrestricted direct read/write access .

DPC.1 to DPC.0

(SDPS1, SDPS0)

Source Data Pointer Select Bits 1:0. These bits select one of the three data pointers

as the active source pointer for the load operation . A new data pointer must be selected

before being used to read data memory:

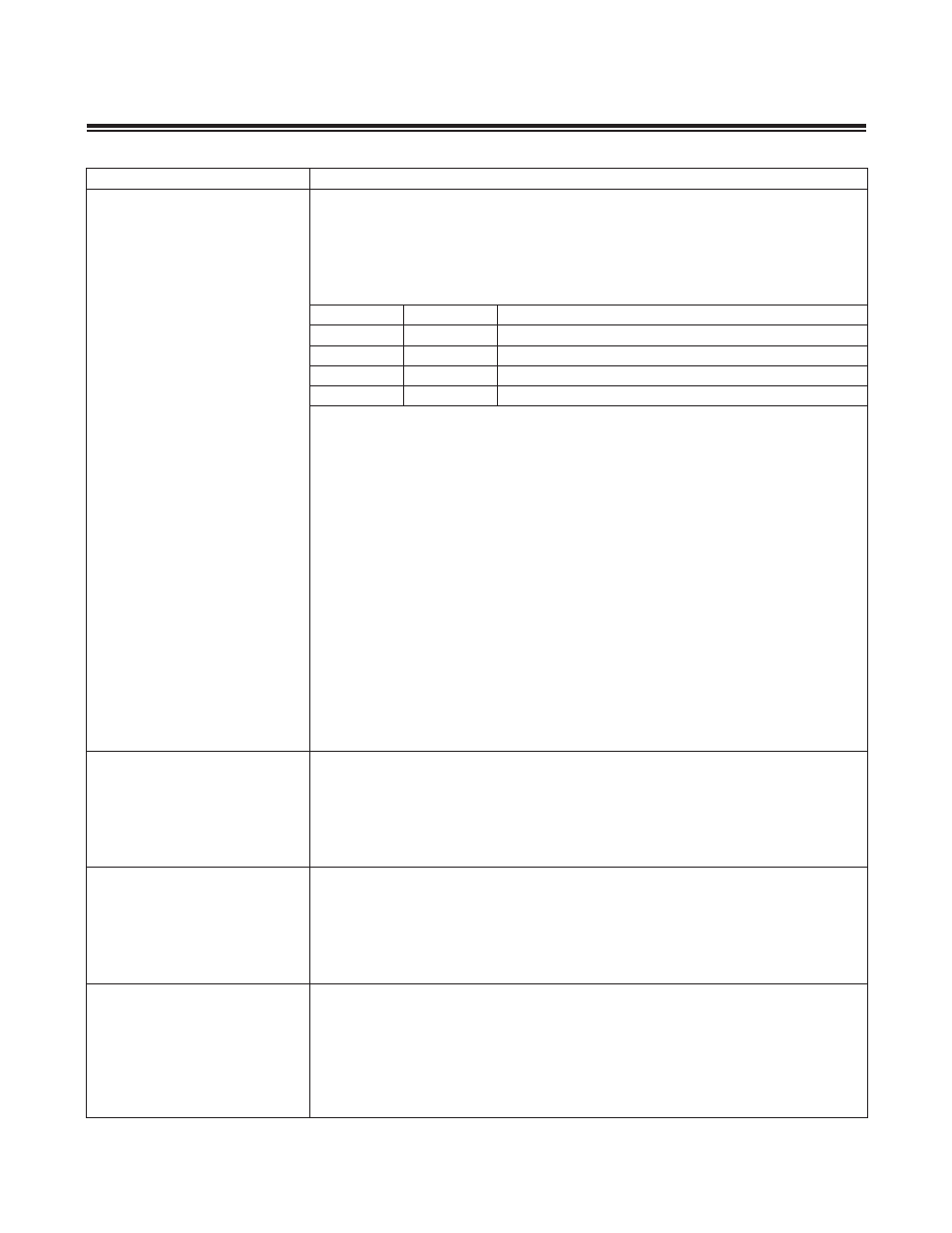

SDPS1

SDPS0

SOURCE POINTER SELECTION

0

0

DP[0]

0

1

DP[1]

1

0

FP (BP[OFFS])

1

1

Reserved (select FP if set)

These bits default to 00b but do not activate DP[0] as an active source pointer until the

SDPS bits are explicitly cleared to 00b or the DP[0] register is written by an instruction . Also,

modifying the register contents of a data/frame pointer register (DP[0], DP[1], BP or OFFS)

changes the setting of the SDPS bits to reflect the active source pointer selection .

DPC.2 (WBS0)

Word/Byte Select 0. This bit selects access mode for DP[0] . When WBS0 is set to 1, the

DP[0] is operated in word mode for data memory access; when WBS0 is cleared to 0,

DP[0] is operated in byte mode for data memory access .

DPC.3 (WBS1)

Word/Byte Select 1. This bit selects access mode for DP[1] . When WBS1 is set to 1, the

DP[1] is operated in word mode for data memory access; when WBS1 is cleared to 0,

DP[1] is operated in byte mode for data memory access .

DPC.4 (WBS2)

Word/Byte Select 2. This bit selects access mode for BP[OFFS] . When WBS2 is set to 1,

the BP[OFFS] is operated in word mode for data memory access; when WBS2 is cleared

to 0, BP[OFFS] is operated in byte mode for data memory access .

DPC.5

Reserved . Reads return 0 .

DPC.6 (CWBS)

Code Pointer Word/Byte Select. This bit selects access mode for the code pointer, CP .

When CWBS is set to 1, the CP is operated in word mode for data memory access; when

CWBS is cleared to 0, CP is operated in byte mode for data memory access .

DPC.15 to DPC.7

Reserved . Read returns 0 .

GR, 0Eh[05h]

General Register (16 bits)

Initialization

This register is cleared to 0000h on all forms of reset .

Access

Unrestricted direct read/write access .

GR.15 to GR.0

This register is intended primarily for supporting byte operations on 16-bit data . The 16-bit

register is byte-readable, byte-writable through the corresponding GRL and GRH 8-bit reg-

isters and byte-swappable through the GRS 16-bit register

GRL, 0Eh[06h]

General Register Low Byte (8 bits)

Initialization

This register is cleared to 00h on all forms of reset .

Access

Unrestricted direct read/write access .

GRL.7 to GRL.0

This register reflects the low byte of the GR register and is intended primarily for support-

ing byte operations on 16-bit data . Any data written to the GRL register is also stored in

the low byte of the GR register .

BP, 0Eh[07h]

Frame Pointer Base Register (16 bits)

Initialization

This register is cleared to 0000h on all forms of reset .

Access

Unrestricted direct read/write access .

BP.15 to BP.0

This register serves as the base pointer for the frame pointer (FP) . The frame pointer is

formed by unsigned addition of frame pointer base register (BP) and frame pointer offset

register (OFFS) . The content of this base pointer register is not affected by increment/dec-

rement operations performed on the offset (OFFS) register .