Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 70

4-15

MAXQ610 User’s Guide

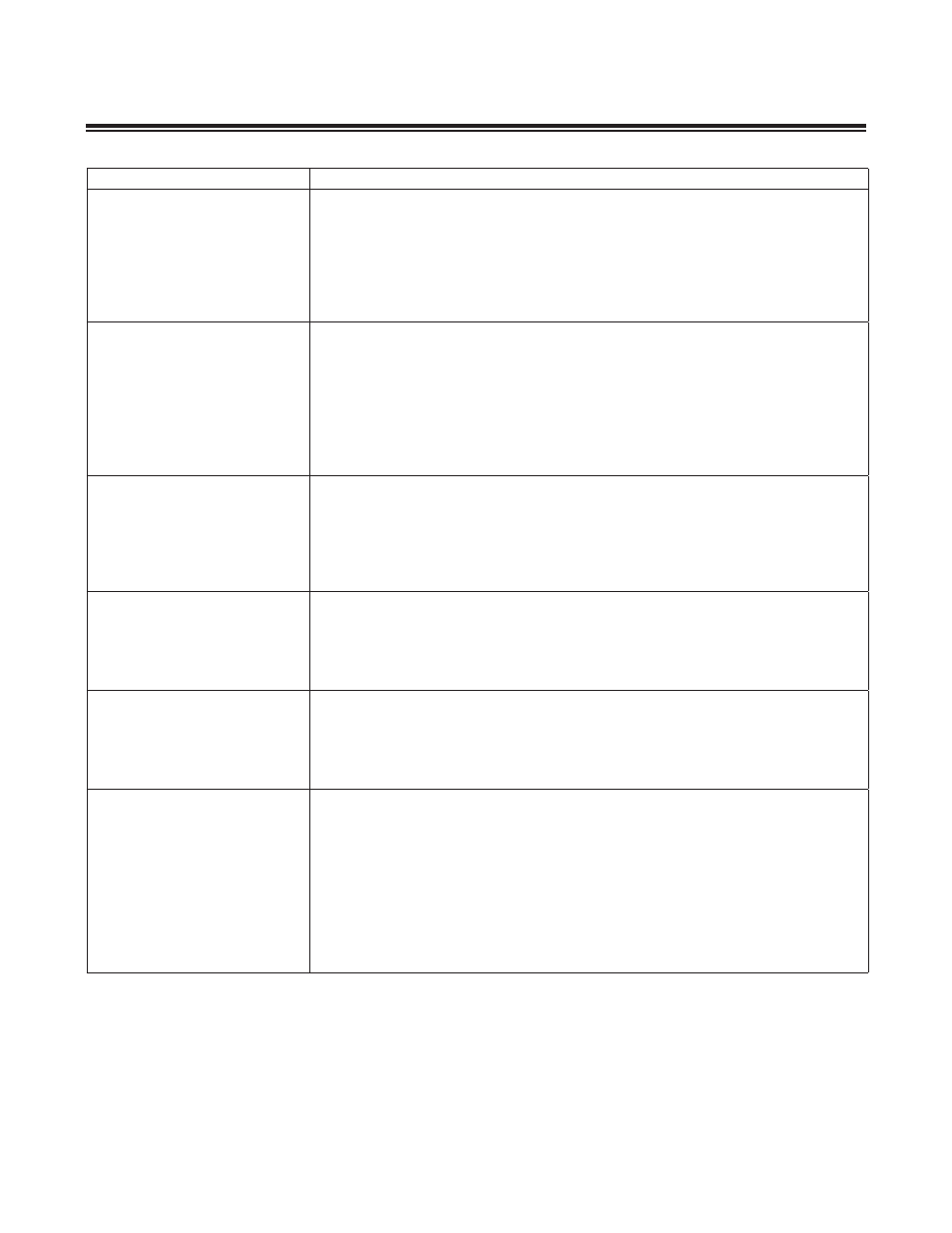

REGISTER

DESCRIPTION

IP, 0Ch[00h]

Instruction Pointer Register (16 bits)

Initialization

This register is cleared to 8000h on all forms of reset .

Access

Unrestricted direct read/write access .

IP.15 to IP.0

This register contains the address of the next instruction to be executed and is automati-

cally incremented by 1 after each program fetch .

Writing an address value to this register causes program flow to jump to that address .

Reading from this register does not affect program flow .

SP, 0Dh[01h]

Stack Pointer Register (16 bits)

Initialization

This register is cleared to 03F0h on all forms of reset .

Access

Unrestricted direct read/write access .

SP.9 to SP.0

These 10 bits indicate the current top (equals the lowest address used) of the soft stack .

This pointer is decremented before a value is pushed on the stack (increasing the stack

depth, MOVE @++SP, …) and incremented after a value is popped from the stack

(decreasing the stack depth, MOVE …, @SP--) .

SP.15 to SP.10

Reserved . Reads return 0 .

IV, 0Dh[02h]

Interrupt Vector Register (16 bits)

Initialization

This register is cleared to 0020h on all forms of reset .

Access

Unrestricted direct read-only .

IV.15 to IV.0

This register contains the address of the interrupt service routine . The interrupt handler

generates a CALL to an offset from this address whenever the corresponding interrupt is

acknowledged .

LC[0], 0Dh[06h]

Loop Counter 0 Register (16 bits)

Initialization

This register is cleared to 0000h on all forms of reset .

Access

Unrestricted direct read/write access .

LC[0].15 to LC[0].0

This register is used as the loop counter for the DJNZ LC[0], src operation . This operation

decrements LC[0] by one and then jumps to the address specified in the instruction by src .

LC[1], 0Dh[07h]

Loop Counter 1 Register (16 bits)

Initialization

This register is cleared to 0000h on all forms of reset .

Access

Unrestricted direct read/write access .

LC[1].15 to LC[1].0

This register is used as the loop counter for the DJNZ LC[1], src operation . This operation

decrements LC[1] by one and then jumps to the address specified in the instruction by src .

OFFS, 0Eh[03h]

Frame Pointer Offset Register (8 bits)

Initialization

This register is cleared to 00h on all forms of reset .

Access

Unrestricted direct read/write access .

OFFS.7 to OFFS.0

This 8-bit register provides the frame pointer (FP) offset from the base pointer (BP) . The

frame pointer is formed by unsigned addition of frame pointer base register (BP) and

frame pointer offset register (OFFS) . The contents of this register can be postincremented

or postdecremented when using the frame pointer for read operations and can be prein-

cremented or predecremented when using the frame pointer for write operations . A carry

out or borrow resulting from an increment/decrement operation has no effect on the frame

pointer base register (BP) .