4 in-circuit debug peripheral registers, 1 in circuit debug temp 0/1 register (icdt0/icdt1), 2 in-circuit debug control register (icdc) – Maxim Integrated MAXQ610 User Manual

Page 162: 12 .4 in-circuit debug peripheral registers -11, Maxq610 user’s guide

12-11

MAXQ610 User’s Guide

• Special caution should be exercised when using the write register command on register bits that globally affect

system operation (e .g ., IGE, STOP) . If the write register command is used to invoke stop mode (setting STOP = 1),

the RESET pin can be asserted to reset the debug engine and return to the background mode of operation .

• Single stepping (trace) through any operation that changes the state of the IGE bit results in the debug engine over-

riding the bit change since it retains the IGE bit setting captured when active debug mode was entered .

• Single stepping (trace) into an operation that sets STOP = 1 when IGE = 1 effectively allows enabled interrupts nor-

mally capable of causing exit from stop mode to do so .

• Data memory allocation is important during system development if in-circuit debug is planned. The top 32 bytes

(16 words) of data memory are used by the debug service routine during debug mode . The data contents in these

locations can be altered and cannot be recovered .

• One available stack location is needed for debug mode. If the stack is full when entering debug mode, the oldest

data in the stack is overwritten .The crystal warmup counter is the only counter not disabled when active debug

mode is entered . If the crystal warmup counter completes while in active debug mode, a glitchless switch is made

to selected clock source (which was being counted) . It is important that the user recognize that this action occurs

since the TAP clock should be run no faster than 1/8th the system clock frequency .

• Any signal sampling that relies upon the internal system clock (e.g., counter inputs) can be unreliable since the

system clock is turned off inside active debug mode between debug mode commands .

• To debug UAPP/ULDR regions their passwords should not be cleared. The following methods can be used for this

purpose:

1) Place the application startup code at the start of the UAPP segment (or)

2) Explicitly add a password to be located at word address 0x2010 (byte address 0x4020) . Only one of the

32 bytes of the password field needs to be programmed to something other than 0xFF or 0x00 .

• The stack plug-in should be disabled for debug commands to be effective.

12.4 In-Circuit Debug Peripheral Registers

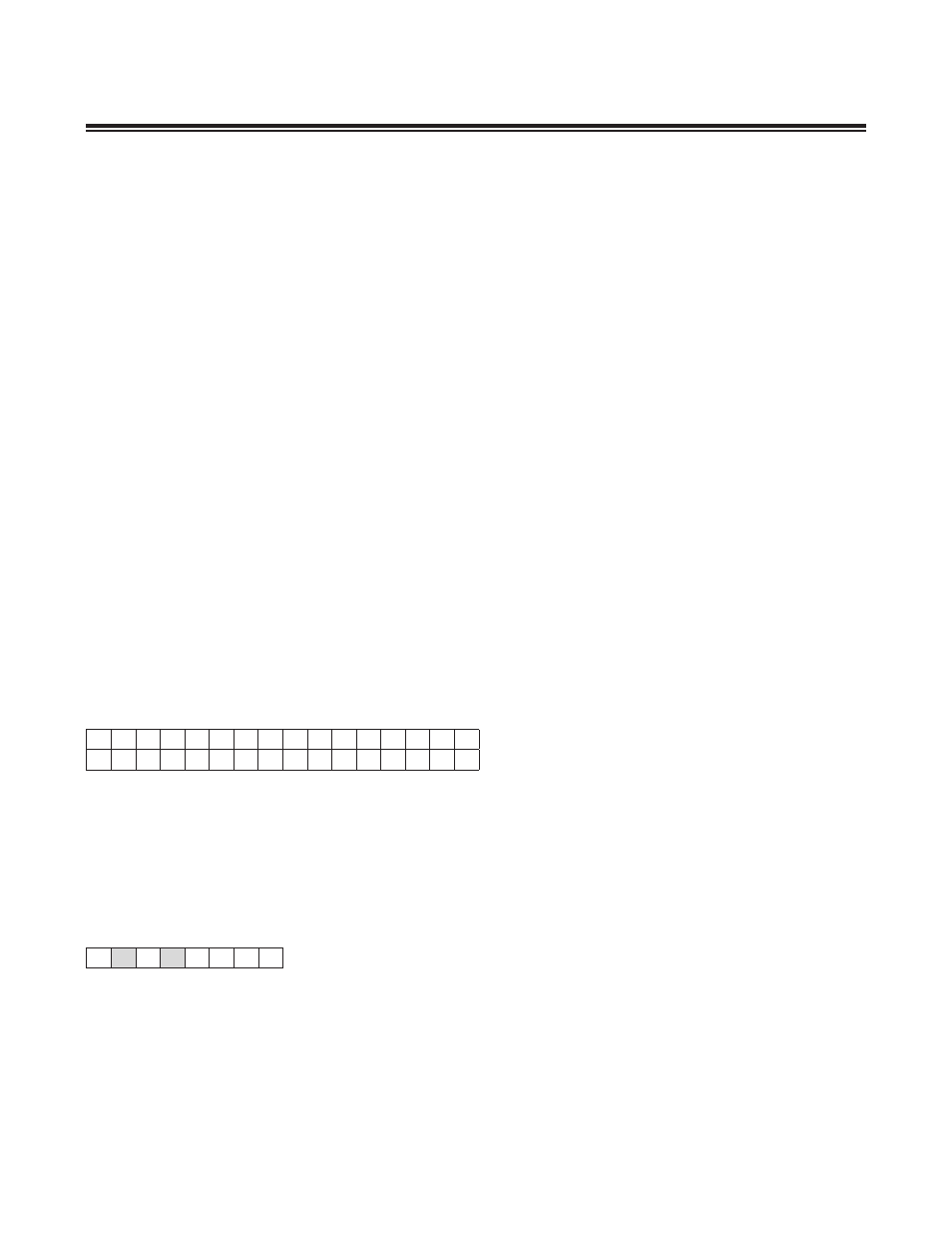

12.4.1 In Circuit Debug Temp 0/1 Register (ICDT0/ICDT1)

These registers are read/write accessible by the CPU only in background mode or debug mode . These registers are

intended for use by the utility ROM routines as temporary storage to save registers that might otherwise have to be

placed in the stack .

12.4.2 In-Circuit Debug Control Register (ICDC)

Bit 7: Debug Mode Enable (DME). When this bit is cleared to 0, background mode commands can be executed, but

breakpoints are disabled . When this bit is set to 1, breakpoints are enabled while background mode commands still

can be entered . This bit cany only be set or cleared from background debug mode . This bit has no meaning for the

utility ROM code .

15

0

In Circuit Debug Temp 0 Register (ICDT0)

In Circuit Debug Temp 1 Register (ICDT1)

0

s

0

s

0

s

0

s

0

s

0

s

0

s

0

s

0

s

0

s

0

s

0

s

0

s

0

s

0

s

0

s

Power-On Reset or Test-Logic-Reset

Read (r), Write (w), or Special (s) access

7

0

—

—

In-Circuit Debug Control Register (ICDC)

0

rs

0

r

0

rs

0

r

0

rs

0

rs

0

rs

0

rs

Power-On Reset or Test-Logic-Reset

Read (r), Write (w), or Special (s) access