1 peripheral register bit descriptions, 5 .1 peripheral register bit descriptions -5, Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 77

5-5

MAXQ610 User’s Guide

5.1 Peripheral Register Bit Descriptions

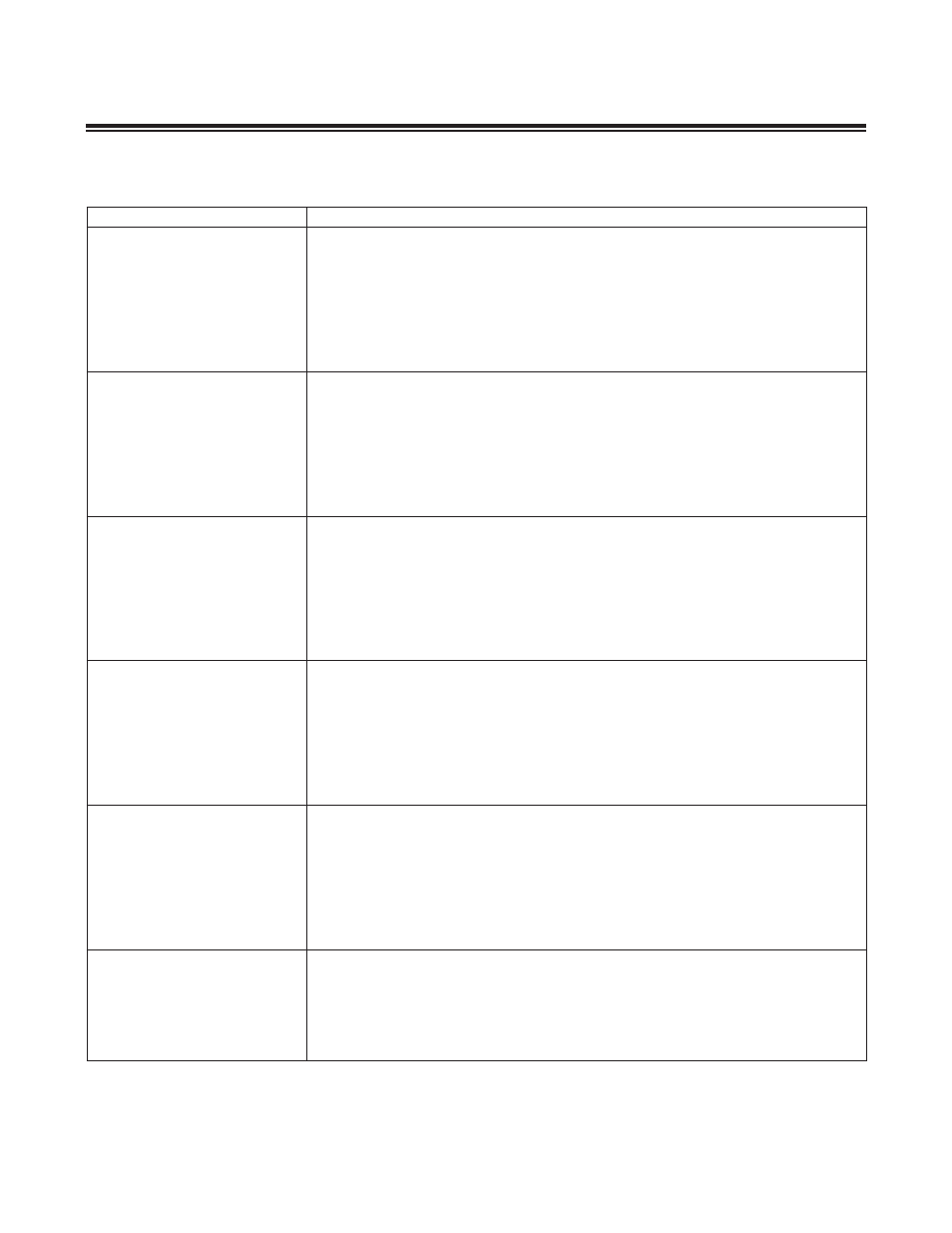

REGISTER

DESCRIPTION

PO0 (00h, 00h)

Port 0 Output Register (8-bit register)

Initialization:

This register is set to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

PO0.7 to PO0.0

Port 0 Output Register Bits 7:0. The PO0 register stores output data for port 0 when it is

defined as an output port and controls whether the internal weak p-channel pullup transistor

is enabled/disabled if a port pin is defined as an input . The contents of this register can be

modified by a write access . Reading from the register returns the contents of the register .

Changing the direction of port 0 does not change the data contents of the register .

PO1 (01h, 00h)

Port 1 Output Register (8-bit register)

Initialization:

This register is set to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

PO1.7 to PO1.0

Port 1 Output Register Bits 7:0. The PO1 register stores output data for port 1 when it is

defined as an output port and controls whether the internal weak p-channel pullup transistor

is enabled/disabled if a port pin is defined as an input . The contents of this register can be

modified by a write access . Reading from the register returns the contents of the register .

Changing the direction of port 1 does not change the data contents of the register .

PO2 (02h, 00h)

Port 2 Output Register (8-bit register)

Initialization:

This register is set to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

PO2.7 to PO2.0

Port 2 Output Register Bits 7:0. The PO2 register stores output data for port 2 when it is

defined as an output port and controls whether the internal weak p-channel pullup transistor

is enabled/disabled if a port pin is defined as an input . The contents of this register can be

modified by a write access . Reading from the register returns the contents of the register .

Changing the direction of port 2 does not change the data contents of the register .

PO3 (03h, 00h)

Port 3 Output Register (8-bit register)

Initialization:

This register is set to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

PO3.7 to PO3.0

Port 3 Output Register Bits 7:0. The PO3 register stores output data for port 3 when it is

defined as an output port and controls whether the internal weak p-channel pullup transistor

is enabled/disabled if a port pin is defined as an input . The contents of this register can be

modified by a write access . Reading from the register returns the contents of the register .

Changing the direction of port 3 does not change the data contents of the register .

EIF0 (04h, 00h)

External Interrupt Flag 0 Register

Initialization:

EIF0 is cleared to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

EIF0.7 to EIF0.0 (IE[7:0])

Interrupt Edge Detect Bits 7:0. These bits are set when a negative edge (ITn = 1) or a

positive edge (ITn = 0) is detected on the interrupt pin n . Setting any of the bits to 1 gener-

ates an interrupt to the CPU if the corresponding interrupt is enabled . The bit remains set

until cleared by software or a reset . It must be cleared by software before exiting the inter-

rupt source routine or another interrupt is generated as long as the bit remains set .

EIE0 (05h, 00h)

External Interrupt Enable 0 Register

Initialization:

EIE0 is cleared to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

EIE0.7 to EIE0.0 (EX[7:0])

Enable External Interrupt Bits 7:0. Setting any of these bits to 1 enables the correspond-

ing external interrupt . Clearing any of the bits to 0 disables the corresponding interrupt

function .