7 ir timer peripheral registers, 1 ir control register (ircn), 8 .7 ir timer peripheral registers -10 – Maxim Integrated MAXQ610 User Manual

Page 123: 8 .7 .1 ir control register (ircn) -10, Maxq610 user’s guide

8-10

MAXQ610 User’s Guide

8.7 IR Timer Peripheral Registers

8.7.1 IR Control Register (IRCN)

Bit 13: IRV Count Enable (IRVCEN). Setting this bit to 1, while IRMODE = 0 (receive mode), enables IRV up counting .

IRCFME is used to select the clock source of the IRV in this mode . To use this mode without affecting the IRTX pin,

keep IREN = 0 .

Bits 12 to 10: IR Clock Divide Bits [1:0] (IRDIV[2:0]). These two bits select the divide ratio for the IR input clock .

Bits 9 and 8: IR Envelope Mode Bits [1:0] (IRENV[1:0]). Setting either of these bits (but not both) to 1 enables the

envelope modulation signal (based upon the IRDATA and IRTXPOL bits) to be output separately to the IRTXM pin dur-

ing transmit mode . When these bits are both cleared to 0 or set to 1, the standard internal modulation is performed

during IR transmit mode and the envelope signal is not output to the IRTXM pin . When the envelope mode is enabled,

it is possible to output either the modulated or unmodulated carrier to the IRTX pin (see the following table) .

Bit 7: IR Receive Reload Enable (IRXRL). Setting this bit to 1 enables automatic reload of the IRV register with 0000h

whenever a qualified edge event capture occurs during the IR receive operation . If IRXRL = 0, the IRV register is not

reloaded with 0000h, but continues running during the IR receive operation .

Bit 6: IR Carrier Frequency Measure Enable (IRCFME). Setting this bit to 1 enables direct clocking of the IRV

register using the defined IRCLK during the IR receive operation . Clearing this bit to 0 results in IRV counting of the

IRCA-defined carrier during the receive operation . Using IRCFME = 1 allows system clock resolution when capturing,

whereas IRCFME = 0 allows only (Sysclk/2) resolution when IRCA = 0000h .

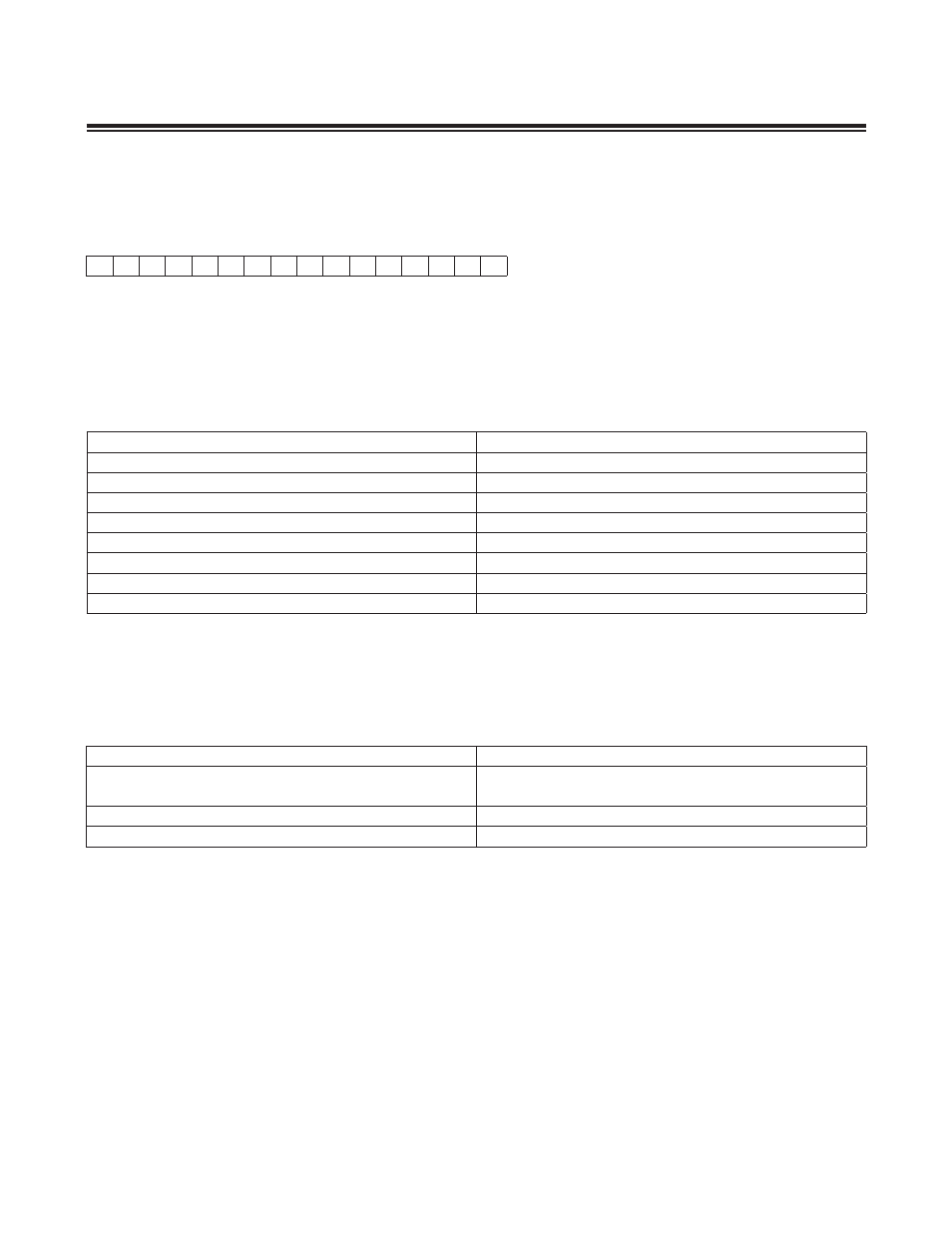

15

0

IR Control Register (IRCN)

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

0

rw

Power-On Reset and System Resets

Read (r), Write (w), or Special (s) access

IRDIV[2:0]

IR INPUT CLOCK-DIVIDE RATIO

000

f

SYSCLK

/1

001

f

SYSCLK

/2

010

f

SYSCLK

/4

011

f

SYSCLK

/8

100

f

SYSCLK

/16

101

f

SYSCLK

/32

110

f

SYSCLK

/64

111

f

SYSCLK

/128

IRENV[1:0]

IRTX OUTPUT

00 or 11

Envelope mode disabled .

Standard IRTX modulation (default) .

01

Standard IRTX modulation .

10

Constant IRTX carrier (unmodulated) .