3 internal system clock generation, 8 wake-up timer, 1 using the wake-up timer to exit stop mode – Maxim Integrated MAXQ610 User Manual

Page 28: 9 interrupts, 1 servicing interrupts, 2 .7 .3 internal system clock generation -24, 2 .8 wake-up timer -24, 2 .9 interrupts -24, 2 .9 .1 servicing interrupts -24, Table 2-6 . system clock rate control settings -24

2-24

MAXQ610 User’s Guide

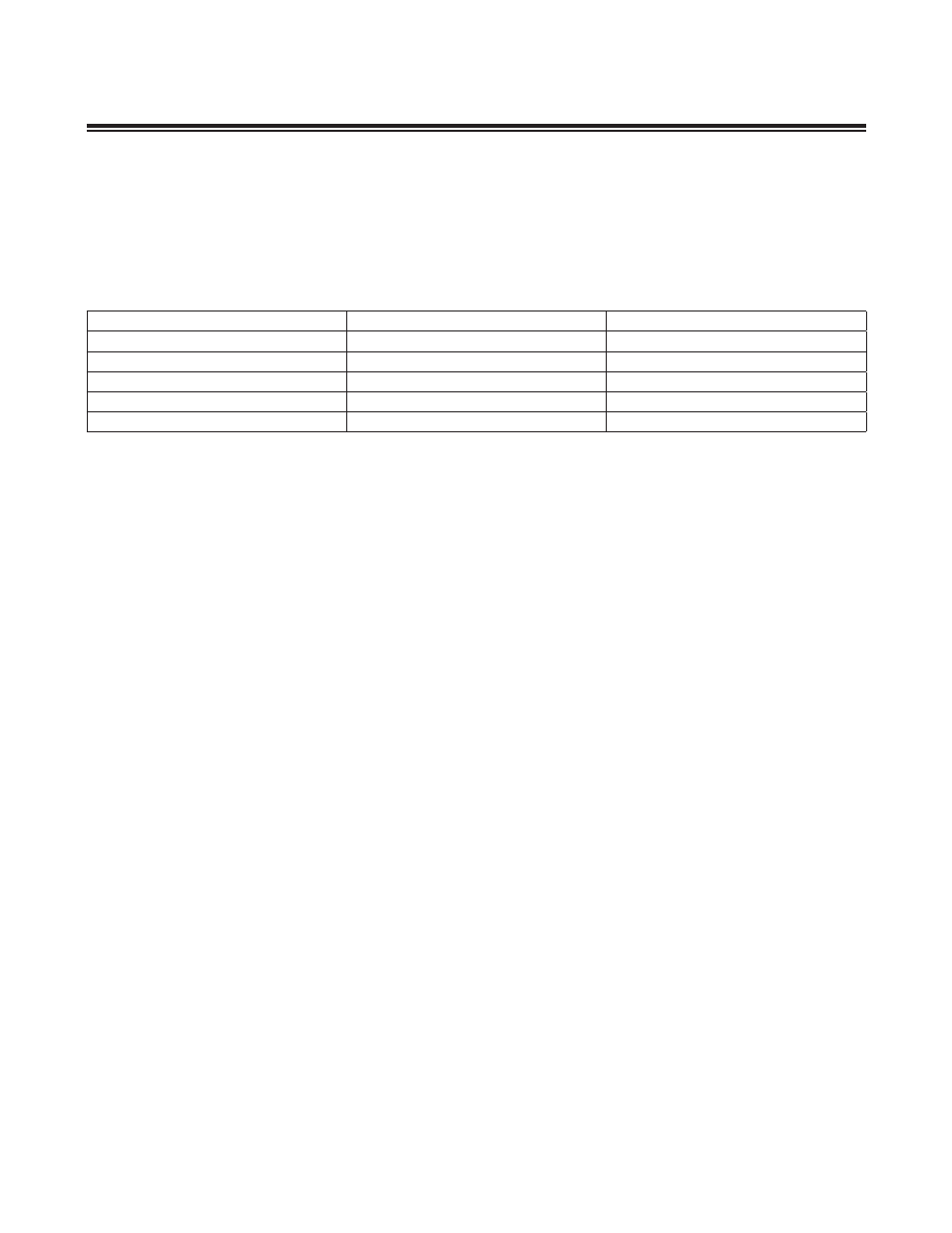

2.7.3 Internal System Clock Generation

The internal system clock is derived from the currently selected oscillator input . By default, one system clock cycle is

generated per oscillator cycle, but the number of oscillator cycles per system clock can also be increased by setting

the power-management mode enable (PMME) bit and the clock-divide control (CD[1:0]) register bits according to

Table 2-6 .

2.8 Wake-Up Timer

The MAXQ610 provides a simple wake-up timer that can trigger an interrupt after a user-definable number of internal

8kHz ring cycles . Since the wake-up timer is running off the internal ring and keeps running even during stop mode, it

can be used to wake the MAXQ610 up from stop mode at periodic intervals .

To use the wake-up timer, the WUT register should be written first (before the wake-up timer is started) to define the

countdown interval . Once the time interval has been defined, the wake-up timer can be started by setting the WTE bit

to 1 . The time interval until the wake-up timer counts down to zero is defined by:

f

NANO

x WUT[15:0]

With the maximum possible time interval being:

f

NANO

x (2

16

- 1)

2.8.1 Using the Wake-Up Timer to Exit Stop Mode

To use the wake-up timer to exit stop mode after a predefined period of time, the following conditions must be met

before entering stop mode:

• The WUT register must be written to define the countdown interval value.

• The WTE bit must be written to 1 to start the wake-up timer.

• The IGE (IC.0) bit must be set to 1 to enable global interrupts. The wake-up timer cannot wake the MAXQ610 up

from stop mode if its interrupt does not fire .

2.9 Interrupts

The MAXQ610 provides a hardware interrupt handler with interrupt vector (IV) table base address register and the

interrupt control (IC) register . The IV register is fixed at 0020h and acts as the vector table base location . Interrupts

can be generated from system level sources (e .g ., watchdog timer) or by sources associated the peripheral modules .

The interrupt vectors are preset at eight fixed memory address offsets from IV with hardware priority control that can

be programmed through the interrupt priority register zero (IPR0) .

2.9.1 Servicing Interrupts

For the MAXQ610 to service an interrupt, interrupt handling must be enabled globally and locally . The IGE bit located

in the IC register acts as a global interrupt mask that affects all interrupts, with the exception of the power-fail warning

interrupt . This bit defaults to 0, and it must be set to 1 before any interrupt handling takes place .

The local interrupt-enable bit for a particular source is in one of the peripheral registers associated with that peripheral

module or in a system register for any system interrupt source . When an interrupt condition occurs, its individual flag

Table 2-6. System Clock Rate Control Settings

PMME

CD[1:0]

CYCLES PER CLOCK

0

00

1 (default)

0

01

2

0

10

4

0

11

8

1

xx

256