Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 87

5-15

MAXQ610 User’s Guide

REGISTER

DESCRIPTION

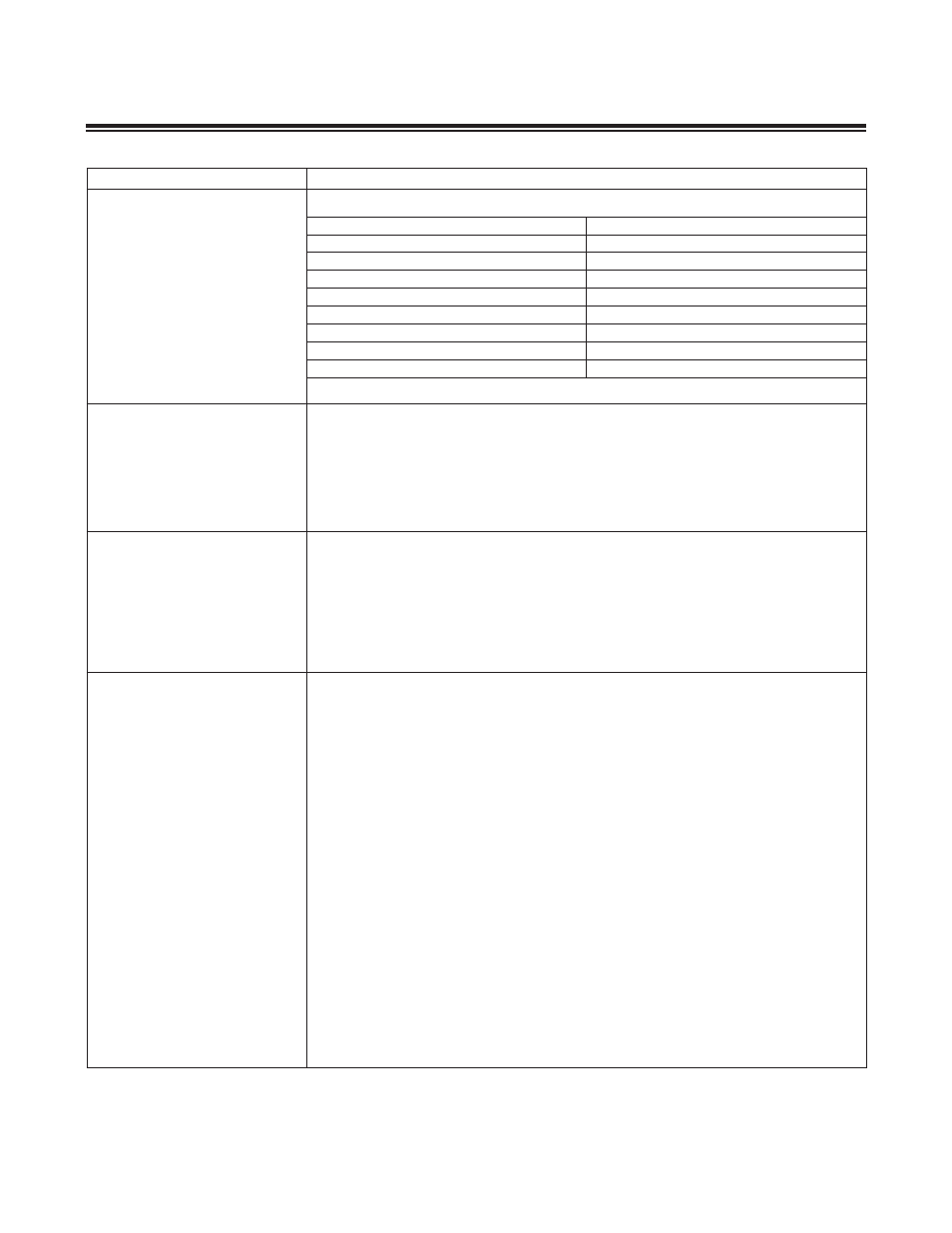

IRCN.12 to IRCN.10 (IRDIV[2:0])

IR Clock Divide Bits. These two bits select the divide ratio for the IR input clock .

IRDIV[2:0]

IR INPUT CLOCK-DIVIDE RATIO

000

f

SYSCLK

/1

001

f

SYSCLK

/2

010

f

SYSCLK

/4

011

f

SYSCLK

/8

100

f

SYSCLK

/16

101

f

SYSCLK

/32

110

f

SYSCLK

/64

111

f

SYSCLK

/128

IRCN.15 to IRCN.13

Reserved . Reads return 0 .

IRCA (05h, 02h)

IR Carrier Register (16-bit register)

Initialization:

This register is cleared to 0000h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

IRCA.7 to IRCA.0 (IRCAL[7:0])

IR Carrier Low Byte Bits 7:0. The IRCAL byte defines the number of IR input clocks during

carrier low time . The carrier low time = IRCAL[7:0] + 1 .

IRCA.15 to IRCA.8 (IRCAH[7:0])

IR Carrier High Byte Bits 7:0. The IRCAH byte defines the number of IR input clocks dur-

ing carrier high time . The carrier high time = IRCAH[7:0] + 1 .

IRMT (06h, 02h)

IR Modulator Time (16-bit register)

Initialization:

This register is cleared to 0000h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

IRMT.15 to IRMT.0

IR Modulator Time Bits 15:0. The IRMT register is a 16-bit register that defines the IRDATA

active time during transmit mode . In receive mode (when RXBCNT = 0), it is used to cap-

ture the IRV value on qualified IRRXSEL edges . In receive mode (when RXBCNT = 1), the

IRMT register increments on detection of selected IRRXSEL edge(s) . When RXBCNT is

changed from 0 to 1, the IRMT register is set to 0001h by hardware .

IRCNB (07h, 02h)

Infrared Control Register B (8-bit register)

Initialization:

This register is cleared to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

IRCNB.0 (IROV)

IR Timer Overflow Flag. This flag is set to 1 when the IR timer overflows from 0FFFFh to

0000h in receive mode . This bit must be cleared to 0 by software once it is set .

IRCNB.1 (IRIF)

IR Interrupt Flag. This flag is set to 1 during transmit when the IR timer reloads its value

and in receive mode (if RXBCNT = 0), when a capture occurs . In receive mode (when

RXBCNT = 1), this flag is set whenever the IRCA*2 interval timer expires . This bit must be

cleared to 0 by software once it is set .

IRCNB.2 (IRIE)

IR Interrupt Enable. Setting this bit to 1 enables an interrupt be generated to the CPU

when the IR timer overflow (IROV) or IR interrupt flag is set (IRIF) . Clearing this bit to 0 dis-

ables IR timer interrupt generation .

IRCNB.3 (RXBCNT)

Receive Carrier Burst-Count Enable. Setting this bit to 1 enables the carrier burst count-

ing mode for the IR timer when operating in receive mode . This bit is not meaningful for

the transmit mode . Whenever software changes RXBCNT from 0 to 1, the IRMT register is

set to 0001h by hardware . When RXBCNT = 1, the IR timer receive mode is modified in the

following ways: 1) The IRV register is not captured to the IRMT register on detection of the

IRRXSEL[1:0] selected edge(s); 2) The IRMT register is incremented on detection of the

IRRXSEL[1:0] selected edge(s); 3) The IRIF flag is no longer set on capture edge detec-

tion; 4) An IRCA x 2 interval timer is enabled and upon expiration the IRIF flag is set . When

RXBCNT = 0, the receive carrier burst-count mode is disabled and normal receive capture

functionality can be used .

IRCNB.7 to IRCNB.4

Reserved . Reads return 0 .