Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 93

5-21

MAXQ610 User’s Guide

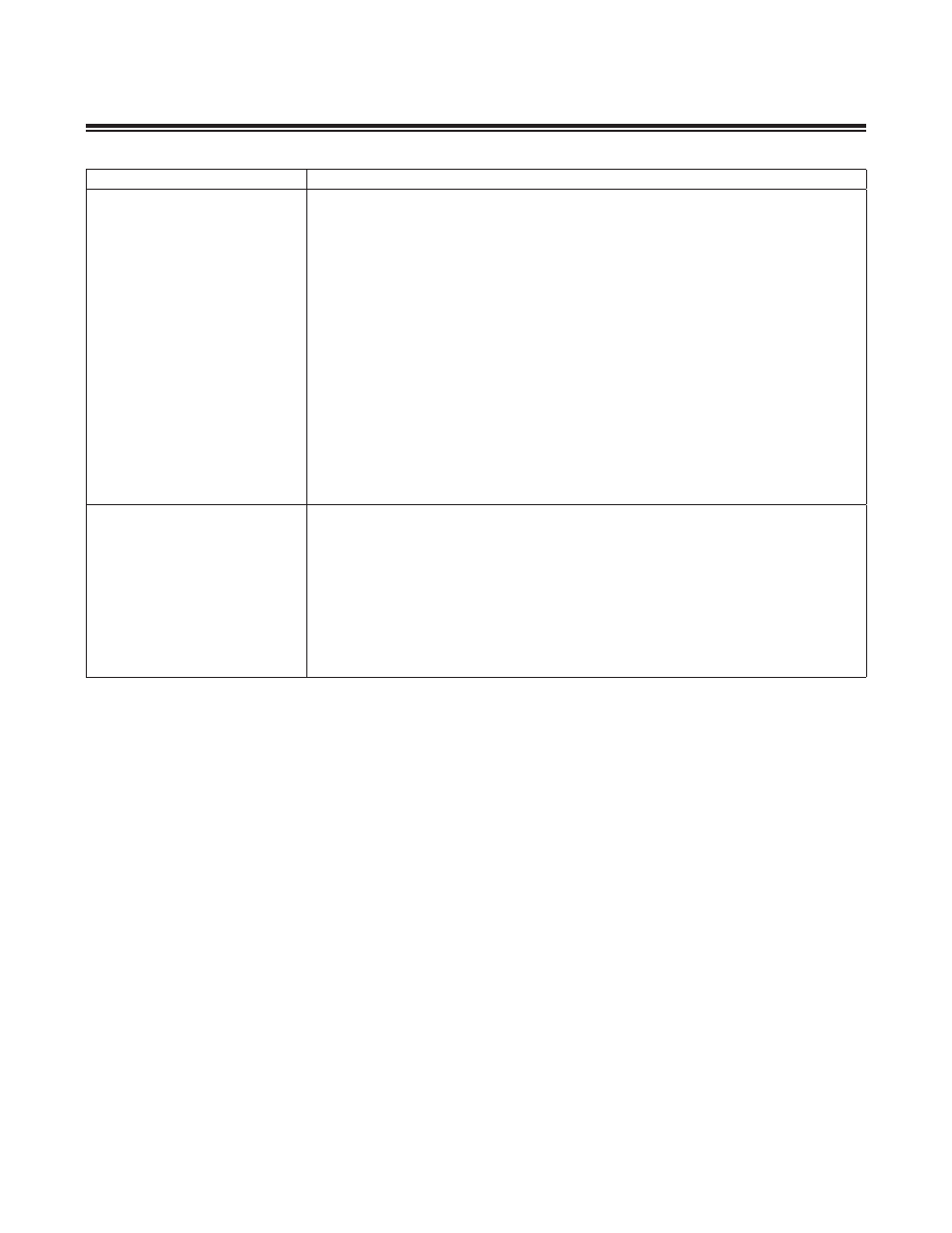

REGISTER

DESCRIPTION

SPICF (0Ch, 03h)

SPI Configuration Register

Initialization:

This buffer is cleared to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

SPICF.0 (CKPOL)

Clock Polarity Select. This bit is used with the CKPHA bit to determine the SPI transfer

format . When the CKPOL is set to 1, the SPI uses the clock falling edge as an active edge .

When the CKPOL is cleared to 0, the SPI selects the clock rising edge as an active edge .

SPICF.1 (CKPHA)

Clock Phase Select . This bit is used with the CKPOL bit to determine the SPI transfer for-

mat . When the CKPHA is set to 1, the SPI samples input data at an inactive edge . When the

CKPHA is cleared to 0, the SPI samples input data at an active edge .

SPICF.2 (CHR)

Character Length Bit. The CHR bit determines the character length for an SPI transfer

cycle . A character can consist 8 or 16 bits in length . When CHR bit is 0, the character is 8

bits; when CHR is set to 1, the character is 16 bits .

SPICF.5 to SPICF.3

Reserved . Reads return 0 .

SPICF.6 (SAS)

Slave Active Select. This bit is used to determine the SSEL active state . When the SAS is

cleared to 0, the SSEL is active low and responds to an external low signal . When the SAS

is set to 1, the SSEL is active high .

SPICF.7 (ESPII)

SPI Interrupt Enable . Setting this bit to 1 enables the SPI interrupt when MODF, WCOL,

ROVR, or SPIC flags are set . Clearing this bit to 0 disables the SPI interrupt .

SPICK (0Dh, 03h)

SPI Clock Register

Initialization:

This buffer is cleared to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

SPICK.7 to SPICK.0 (CKR[7:0])

Clock-Divide Ratio Bits 7:0. These bits select one of the 256 divide ratios (0 to 255) used

for the baud-rate generator, with bit 7 as the most significant bit . The frequency of the SPI

baud rate is calculated using the following equation:

SPI Baud Rate = 0 .5 x System Clock/(divide ratio + 1)

This register has no function when operating in slave mode and the clock generation cir-

cuitry should be disabled .