Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 62

4-7

MAXQ610 User’s Guide

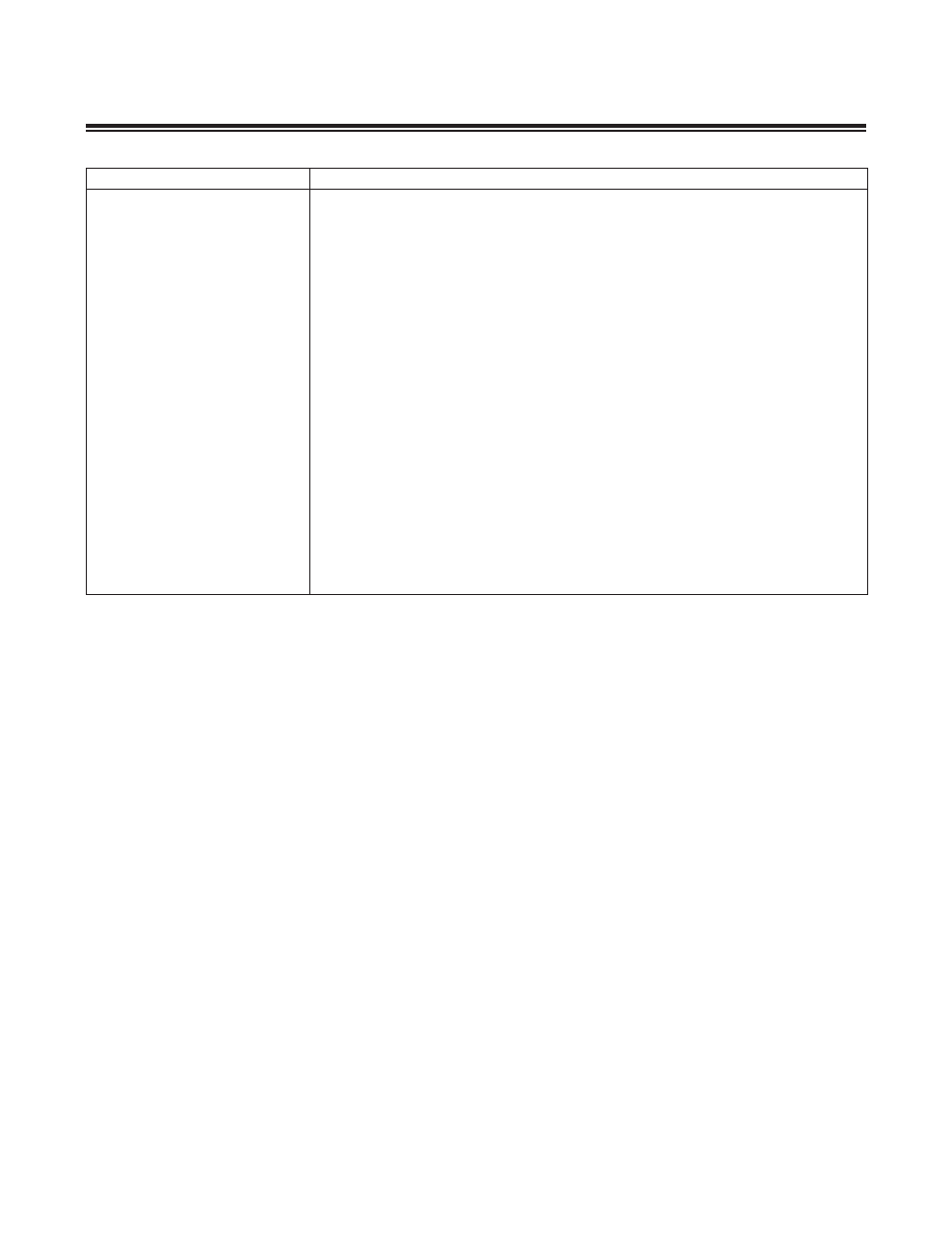

REGISTER

DESCRIPTION

PSF, 08h[04h]

Processor Status Flags Register (8 bits)

Initialization

This register is cleared to 80h on all forms of reset .

Access

Bit 7 (Z) and bit 6 (S) are read-only .

Bits 4, 3 (GPF1, GPF0), bit 2 (OV), bit 1 (C) and bit 0 (E) are unrestricted read/write .

PSF.0 (E)

Equals Flag. This bit flag is set to 1 whenever a compare operation (CMP) returns an

equal result . If a CMP operation returns not equal, this bit is cleared .

PSF.1 (C)

Carry Flag. This bit flag is set to 1 whenever an addition or subtraction operation (ADD,

ADDC, SUB, SUBB) returns a carry or borrow .

This bit flag is cleared to 0 whenever an addition or subtraction operation does not return a

carry or borrow .

PSF.2 (OV)

Overflow Flag. This flag is set to 1 if there is a carry out of bit 14 but not out of bit 15, or

a carry out of bit 15 but not out of bit 14 from the last arithmetic operation, otherwise, the

OV flag remains as 0 . OV indicates a negative number resulted as the sum of two positive

operands, or a positive sum resulted from two negative operands .

PSF.3 (GPF0)

General-Purpose Flag 0

PSF.4 (GPF1)

General-Purpose Flag 1. General-purpose flag bits are provided for user software control .

PSF.5

Reserved . Reads return 0 .

PSF.6 (S)

Sign Flag. This bit flag mirrors the current value of the high bit of the active accumulator

(Acc .15) .

PSF.7 (Z)

Zero Flag. The value of this bit flag equals 1 whenever the active accumulator is equal to

zero, and it equals 0 otherwise .