Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 85

5-13

MAXQ610 User’s Guide

REGISTER

DESCRIPTION

TB0CN.5 (TBOE)

Timer B Output Enable. Setting this bit to 1 enables the clock output function on the TBA

pin if C/TB = 0 . Timer B rollovers do not cause interrupts . Clearing this bit to 0 allows the

TBA pin to function as either a standard port pin or a counter input for Timer B . Timer B 0

and Timer B 1 share the TBA pin . If both timers are configured to generate clock output, the

Timer B 0 clock output special function takes priority over the Timer B 1 clock output .

TB0CN.6 (EXFB)

External Timer B Trigger Flag. When configured as a Timer (C/TB = 0), a negative transi-

When configured as a Timer (C/TB = 0), a negative transi-

tion on the TBB pin causes this flag to be set if (CP/RLB = EXENB = 1) or (CP/RLB = DCEN

= 0 and EXENB = 1) or (CP/RLB = 0 and DCEN = EXENB = 1 and TBCS:TBCR

≠ 00b) .

When CP/RLB = 0 and DCEN = 1 and TBCS:TBCR = 00b, EXFB toggles whenever Timer B

underflows or overflows . Overflow/underflow condition is the same as described for the TFB

bit . In this mode, EXFB can be used as the 17th timer bit and does not cause an interrupt . If

set by a negative transition, this flag must be cleared by software . Setting this bit to 1 forces

a timer interrupt if enabled .

TB0CN.7 (TFB)

Timer B Overflow Flag . This bit is set when Timer B overflows from TBR or the count is

equal to 0000h in down count mode . It must be cleared by software .

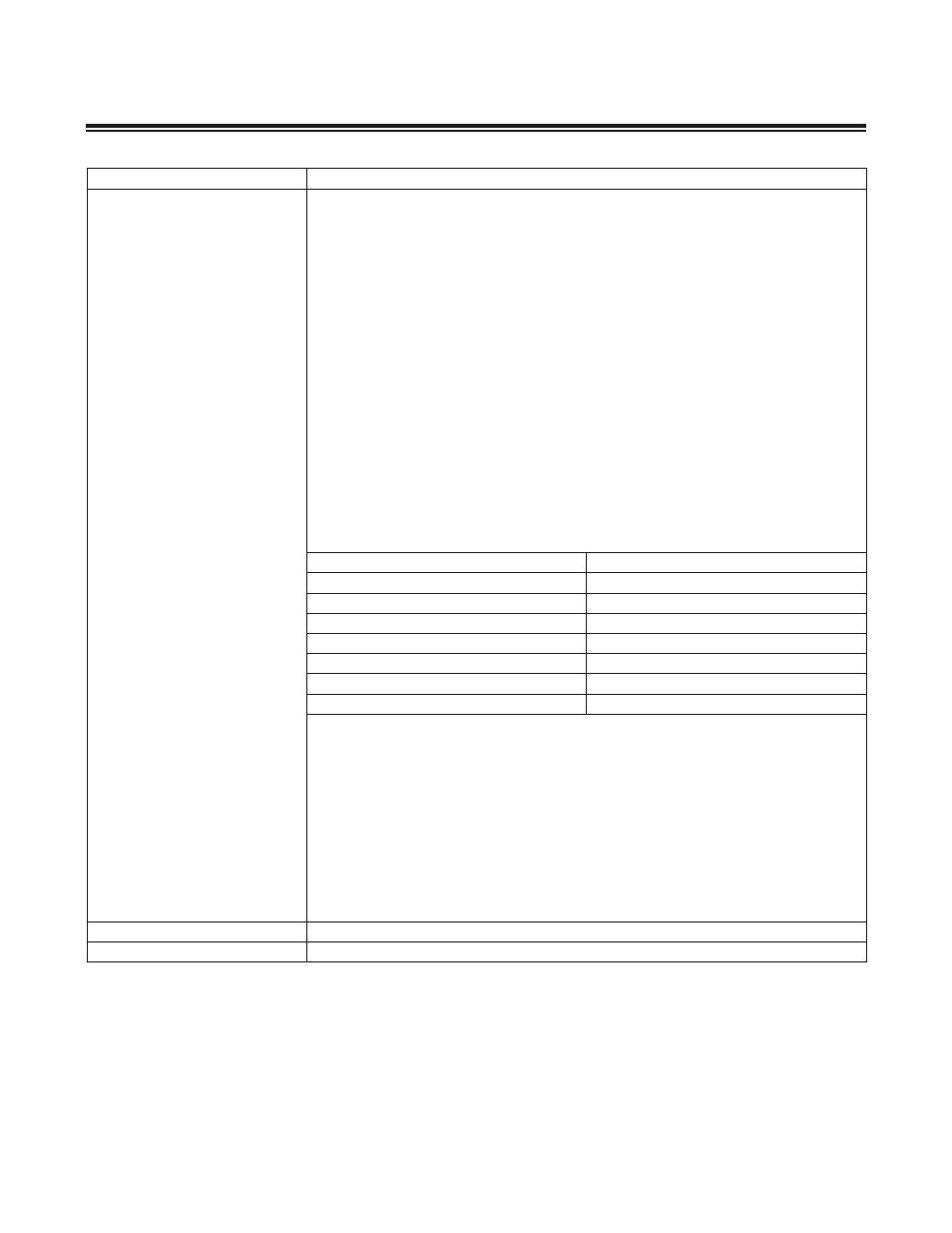

TB0CN.10 to TB0CN.8 (TBPS[2:0]) Timer B Clock Prescaler Bits 2:0 . The TBPS[2:0] bits select the clock prescaler applied

to the system clock input to Timer B . The TBPS[2:0] bits should be configured by the

user when the timer is stopped (TRB = 0) . While hardware does not prevent changing the

TBPS[2:0] bits when the timer is running, the resulting behavior is indeterministic .

Timer B Clock = System Clock/2

(2xTBPS[2:0])

TBPS[2:0]

TIMER B INPUT CLOCK

000

Sysclk/1

001

Sysclk/4

010

Sysclk/16

011

Sysclk/64

100

Sysclk/256

101

Sysclk/1024

11x

Sysclk/1

TB0CN.11 (TBCR)

TBB Pin Output Reset Mode

TB0CN.12 (TBCS)

TBB Pin Output Set Mode. These mode bits define whether the PWM mode output function

is enabled on the TBB pin, the initial output starting state, and what compare mode output

function is in effect . Note that the TBB pin still has certain input functionality when the PWM

output function is enabled . Reference the PWM Output Function section for details on this

mode .

TB0CN.14 to TBCN.13

Reserved . Reads return 0 .

TB0CN.15 (C/TB)

Counter/Timer Select. This bit determines whether Timer B functions as a timer or counter .

Setting this bit to 1 causes Timer B to count negative transitions on the TBA pin . Clearing

this bit to 0 causes Timer B to function as a timer . The speed of Timer B is determined by

the TBPS[2:0] bits of TBCN .

TB1R (02h, 02h)

Timer B Capture/Reload Value Register (see the TB0R register bit description)

TB1CN (03h, 02h)

Timer B Control Register (see the TB0CN register bit description)