Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 65

4-10

MAXQ610 User’s Guide

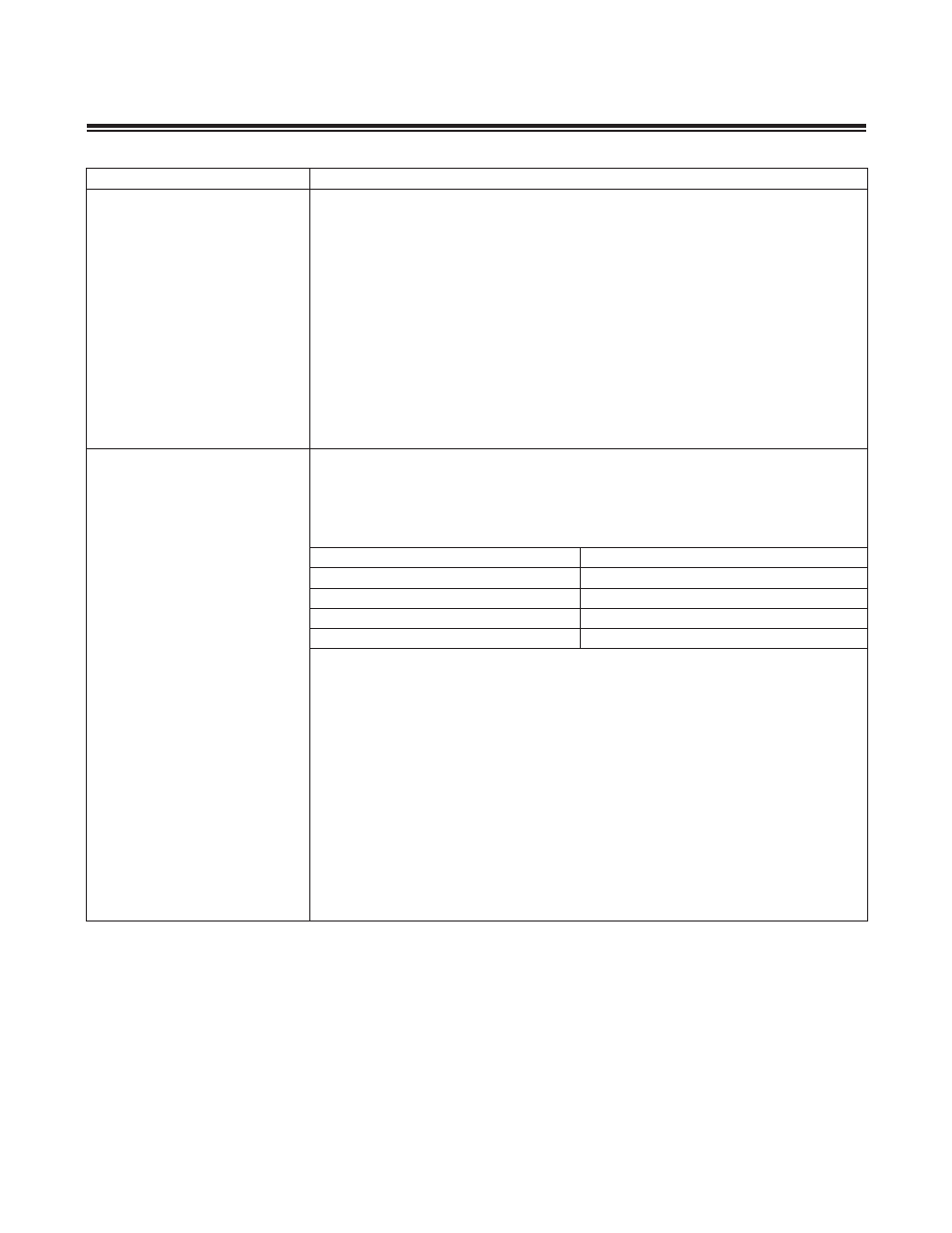

REGISTER

DESCRIPTION

SC.9 (PWLL)

Password Lock User Loader. This bit defaults to 1 on power-fail and power-on reset .

When this bit is 1, it requires a 32-byte password to be matched with the password in the

user loader program space before allowing access to the user loader password-protected

in-circuit debug or bootstrap loader utility ROM routines . Clearing this bit to 0 disables the

password protection for these utility ROM routines . This register bit can only be written

by utility ROM code when PRIV R MEDIUM . ROM-assisted active debug commands are

always disallowed if the value at flash word address 000Eh is programmed (i .e .,

≠FFFFh) .

SC.10 (MPE)

Memory Protection Enable. This bit defaults to 1 on any reset . When this bit is 1, it

enables memory protection and access control . When this bit is 0, no protection-fault

interrupts are generated and any code can access the protected resources . This register

bit can only be changed from 1 to 0 (thereby disabling memory protection) when PRIV =

HIGH . Note that the ability to read utility ROM is always allowed (independent of the MPE

bit state) .

SC.15 to SC.11

Reserved . Reads return 0 .

IPR0, 08h[09h]

Interrupt Priority Register Zero (16 bits)

Initialization

This register is cleared to 0000h on all forms of reset .

Access

Unrestricted direct read/write .

IPR0[1:0] (IVP0[1:0])

Interrupt Vector 0 Priority Bits 1:0. These bits are used to specify the priority level of

interrupt vector 0 .

IVP[1:0]

PRIORITY

00

Level 0 (the highest)

01

Level 1

10

Level 2 (the lowest)

11

Reserved (interrupt disabled)

IPR0[3:2] (IVP1[1:0])

Interrupt Vector 1 Priority Bits 1:0. These bits are used to specify the priority level of

interrupt vector 1 .

IPR0[5:4] (IVP2[1:0])

Interrupt Vector 2 Priority Bits 1:0. These bits are used to specify the priority level of

interrupt vector 2 .

IPR0[7:6] (IVP3[1:0])

Interrupt Vector 3 Priority Bits 1:0. These bits are used to specify the priority level of

interrupt vector 3 .

IPR0[9:8] (IVP4[1:0])

Interrupt Vector 4 Priority Bits 1:0. These bits are used to specify the priority level of

interrupt vector 4 .

IPR0[11:10] (IVP5[1:0])

Interrupt Vector 5 Priority Bits 1:0. These bits are used to specify the priority level of

interrupt vector 5 .

IPR0[13:12] (IVP6[1:0])

Interrupt Vector 6 Priority Bits 1:0. These bits are used to specify the priority level of

interrupt vector 6 .

IPR0[15:14] (IVP7[1:0])

Interrupt Vector 7 Priority Bits 1:0. These bits are used to specify the priority level of

interrupt vector 7 .