Maxq610 user’s guide – Maxim Integrated MAXQ610 User Manual

Page 80

5-8

MAXQ610 User’s Guide

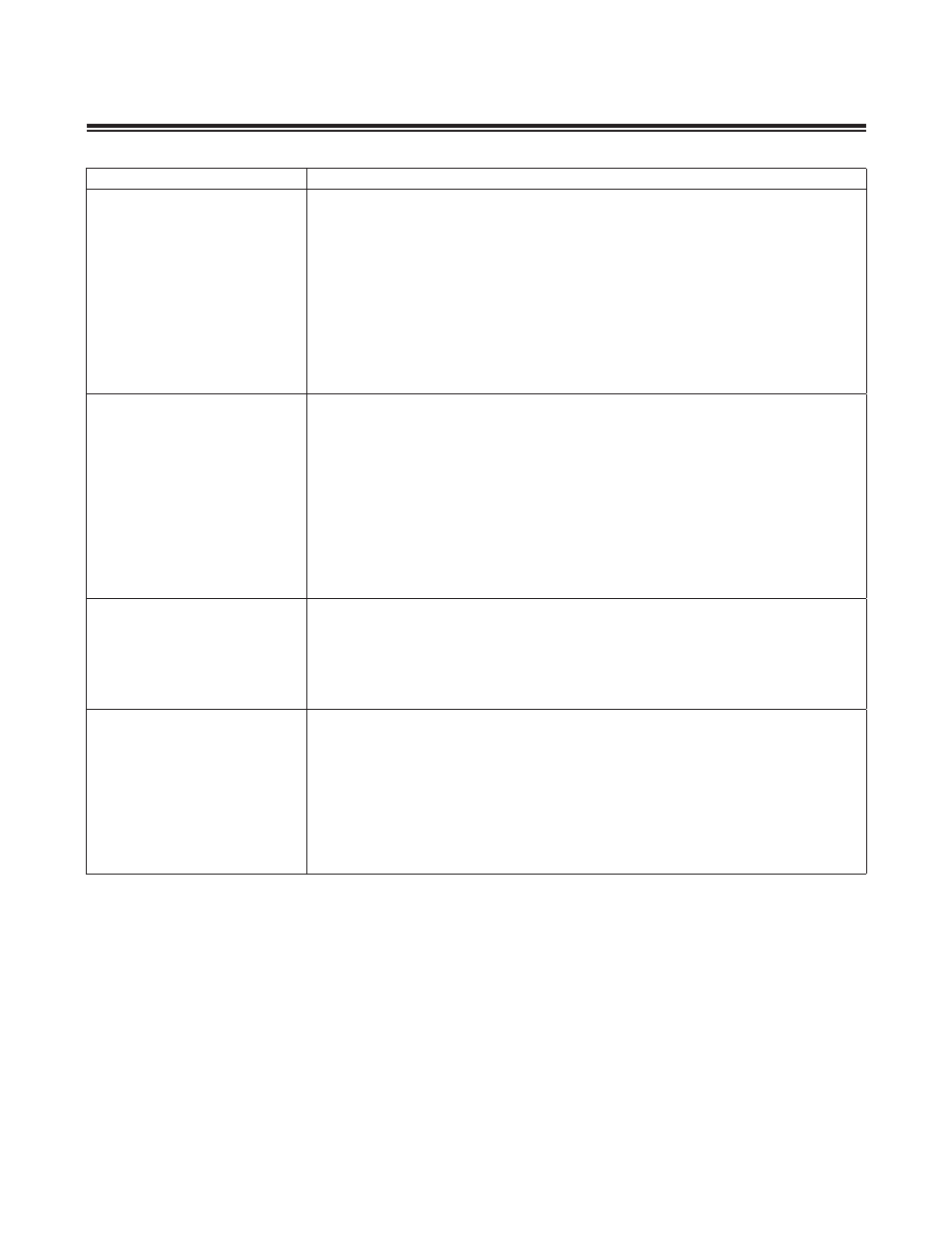

REGISTER

DESCRIPTION

PD2 (12h, 00h)

Port 2 Direction Register

Initialization:

This register is cleared to 00h on all resets except power-fail reset . This register is unaf-

fected by power-fail reset .

Read/Write Access:

Unrestricted read/write .

PD2.7 to PD2.0

Port 2 Direction Register Bits 7:0. PD2 is used to determine the direction of the port 2

function . The port pins are independently controlled by their direction bit . When a bit is set

to 1, its corresponding pin is used as an output; data in the PO register is driven on the pin .

When a bit is cleared to 0, its corresponding pin is used as an input, and allows an external

signal to drive the pin . Note that each port pin has a weak pullup circuit when functioning

as an input and the p-channel pullup transistor is controlled by its respective PO bits . If the

PO bit is set to 1, the weak pullup is on, if the PO bit is cleared to 0, the weak pullup is off

and forces the port pin into three-state .

PD3 (13h, 00h)

Port 3 Direction Register

Initialization:

This register is cleared to 00h on all resets except power-fail reset . This register is unaf-

fected by power-fail reset .

Read/Write Access:

Unrestricted read/write .

PD3.7 to PD3.0

Port 3 Direction Register Bits 7:0. PD3 is used to determine the direction of the port 3

function . The port pins are independently controlled by their direction bit . When a bit is set

to 1, its corresponding pin is used as an output; data in the PO register is driven on the pin .

When a bit is cleared to 0, its corresponding pin is used as an input, and allows an external

signal to drive the pin . Note that each port pin has a weak pullup circuit when functioning

as an input and the p-channel pullup transistor is controlled by its respective PO bits . If the

PO bit is set to 1, the weak pullup is on, if the PO bit is cleared to 0, the weak pullup is off

and forces the port pin into three-state .

CHPREV (13h, 00h)

Chip Revision Register (16-bit register)

Initialization:

The reset value of this register is dependent on the revision of the chip .

Read/Write Access:

Unrestricted read-only .

CHPREV.7 to CHPREV.0

Chip Revision ID Register Bits 7:0. The register is used to provide chip revision informa-

tion . Read accesses return the chip revision in the lower byte and 00h in the upper byte

(e .g ., 00A1h) .

PO4 (00h, 01h)

Port 4 Output Register (8-bit register)

Initialization:

This register is set to 00h on all forms of reset .

Read/Write Access:

Unrestricted read/write .

PO4.5 to PO4.0

Port 4 Output Register Bits 5:0. The PO4 register stores output data for port 4 when it is

defined as an output port and controls whether the internal weak p-channel pullup transistor

is enabled/disabled if a port pin is defined as an input . The contents of this register can be

modified by a write access . Reading from the register returns the contents of the register .

Changing the direction of port 4 does not change the data contents of the register .

PO4.7 to PO4.6

Reserved . Reads return 0 .