Interrupts – Rockwell Automation 1398-PDM-xxx IQ Master Version 3.2.4 for IA-2000 and IQ-5000 Positioning Drive Modules, IQ-55 User Manual

Page 327

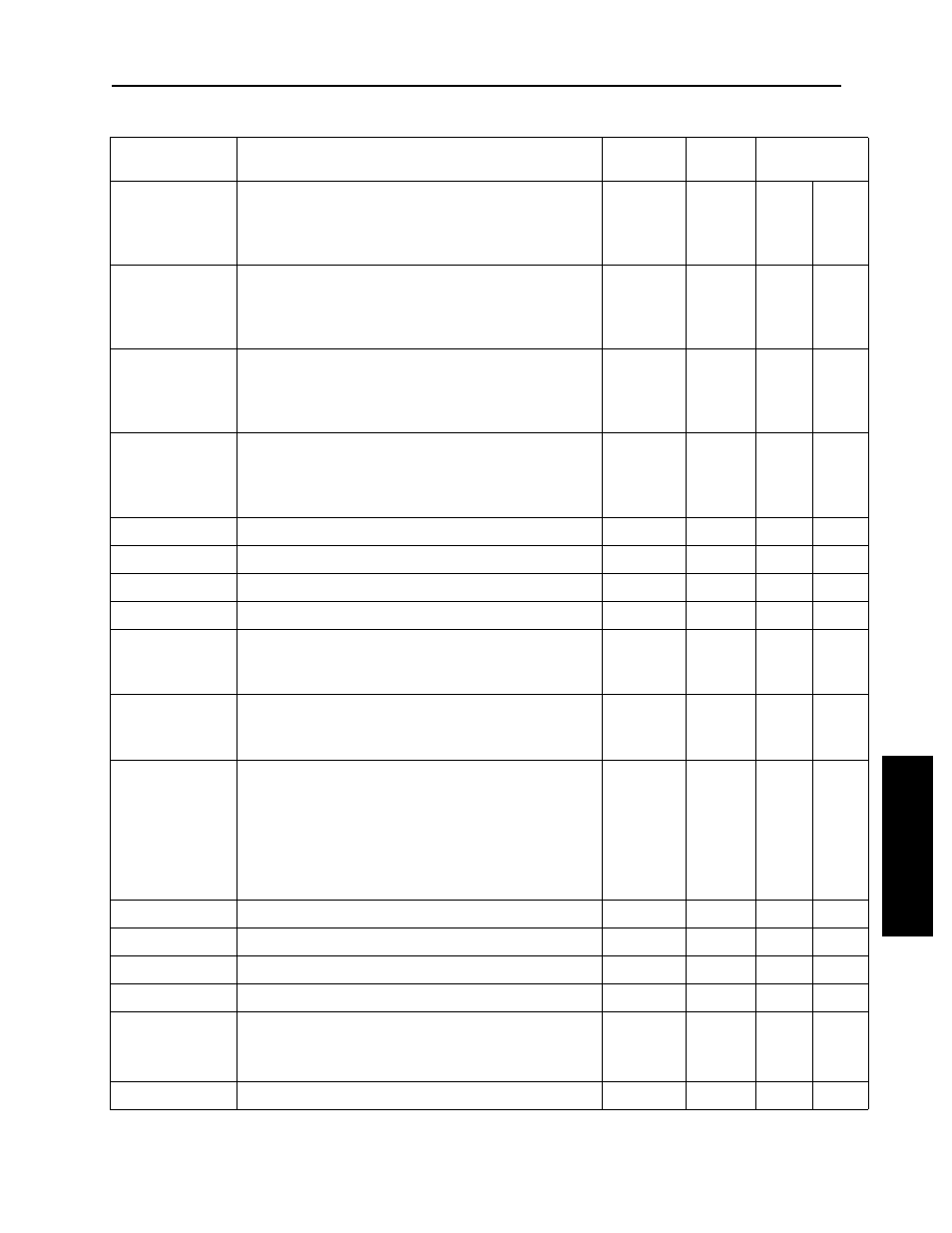

Variables and Flags Assignment and Request Commands • Interrupts

305

Publication 1398-PM601A-EN-P — October 2000

HOST M

O

DE

Interrupts

Command

Description

Flag/

Variable

Read/

Write

Personality

Module

FI1

TRUE if INT1 interrupt received. If TRUE, the I1P1,

I1P2 positions are available. It is your responsibility to

clear these flags. (See SI, INT1, INT2, I1P1, I1P2,

I2P1, I2P2.)

F

R/W

N

FI2

TRUE if INT2 interrupt received. If TRUE, the I2P1,

I2P2 positions are available. It is your responsibility to

clear these flags. (See SI, INT1, INT2, I1P1, I1P2,

I2P1, I2P2.)

F

R/W

N

FIDX1

TRUE if Encoder 1 Index interrupt received. If TRUE,

the IX1P1, IX1P2 positions are available. It is your

responsibility to clear these flags. (See SI, IDX1,

IDX2, IX1P1, IX1P2, IX2P1, IX2P2.)

F

R/W

N

FIDX2

TRUE if Encoder 2 Index interrupt received. If TRUE,

the IX2P1, IX2P2 positions are available. It is your

responsibility to clear these flags. (See SI, IDX1,

IDX2, IX1P1, IX1P2, IX2P1, IX2P2.)

F

R/W

N

I1P1

Position 1 latched by interrupt 1 in user units.

V

R

N

I1P2

Position 2 latched by interrupt 1 in user units.

V

R

N

I2P1

Position 1 latched by interrupt 2 in user units.

V

R

N

I2P2

Position 2 latched by interrupt 2 in user units.

V

R

N

IDX1

TRUE if Encoder 1 Index interrupt is enabled. Inter-

nally set FALSE upon receiving the corresponding

index interrupt. (See FIDX1.)

F

R/W

N

IDX2

TRUE if Encoder 2 Index interrupt is enabled. Inter-

nally set FALSE upon receiving the corresponding

index interrupt. (See FIDX2.)

F

R/W

N

INT1

INT2

The value of these variables indicate the enabled sta-

tus of interrupt inputs one and two. The value will be 0

if the interrupt is disabled, 1 if it is enabled in a one-

shot mode, and 2 if enabled in a continuous mode.

When enabled in a one- shot mode, the variable will

be zeroed (interrupt disabled) upon receiving an inter-

rupt. (See SI, FI1, FI2, I1P1, I1P2, I2P1, I2P2.)

byte

R/W

N

IX1P1

Position 1 latched by Encoder 1 index interrupt.

V

R

N

IX1P2

Position 2 latched by Encoder 1 index interrupt.

V

R

N

IX2P1

Position 1 latched by Encoder 2 index interrupt.

V

R

N

IX2P2

Position 2 latched by Encoder 2 index interrupt.

V

R

N

LP2EN

TRUE for latch position (LPOS) from encoder 2.

Note: Power must be cycled or a Hard reset performed

before latched position selection will take effect.

F

R/W

Y

LPOS

Hardware latched position in user units.

V

R

N