Rockwell Automation 57C570 AutoMax PC3000 User Manual User Manual

Page 188

18Ć6

Registers

Description

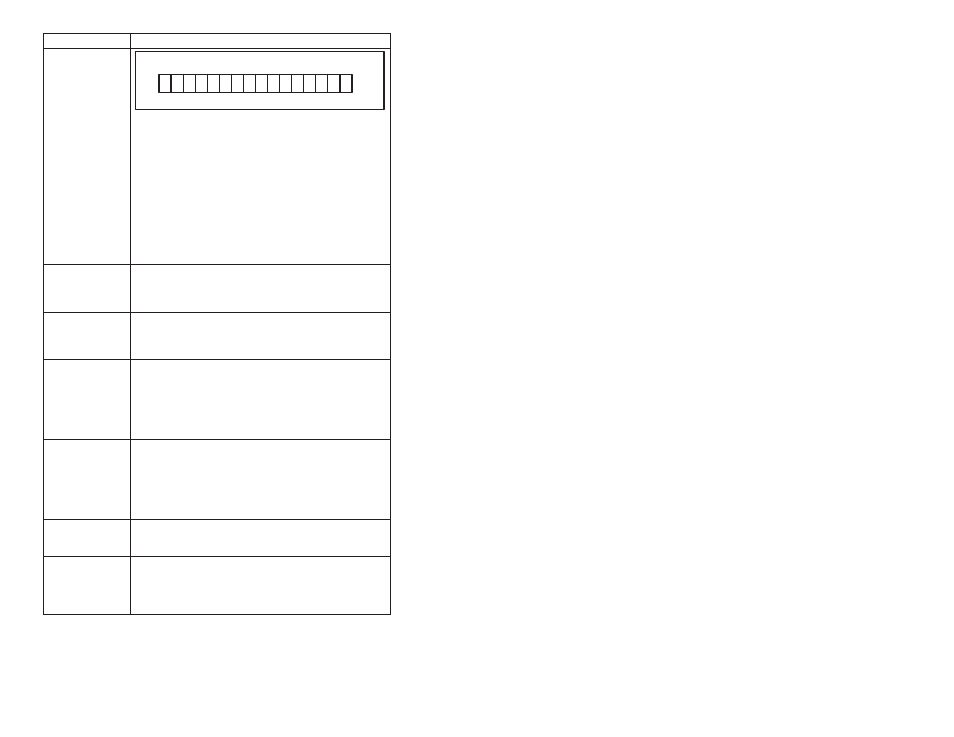

Registers 4 Ć 7

(Drop Status Bits)

(Continued)

0 0

15 14

0 0

13 12

0 0

11 10

0 0

9 8

0 0

7 6

0 1

5 4

1 1

3 2

0 1

1 0

Figure 18.2 Ć Register 4 in Drop 02 Slave Module

Indicating Drops 2, 3, and 4 Actively

Communicating With Master

At powerĆup, the Processor sets the drop depth of the

slaves to 1" to permit remote access to the Processor.

The drop 0 status bit in the slaves and the drop status bits

in the master will not be set.

After a user application task has defined drop depth, the

status bits in the slaves will be set to indicate the drops it

represents. The drop 0 status bit will also be set. In the

master, the drop status bits will be set to indicate all active

drops on the network.

Register 12 Ć

Drop Number

This register stores the drop number you set with the

Change Drop command. See section 12.3.2 for more

information about changing the drop. Bit 15 is set when a

valid drop number is assigned.

Register 14 Ć

Messages

Received

This register reflects the total number of messages

received by that module. While the line is inactive, this

value will remain unchanged. While the line is active, it will

constantly increase to 65535 and then roll over to zero.

Register 15 Ć

Receive Timeouts

When an active drop on the network is set up to receive, a

timer is set. If a message is not received before the timer

expires, a receive timeout occurs and is logged in this

register. The system allows for four consecutive timeouts

before it writes fault code C" to error code register 2001

in the Application Interface or on the Processor Info.

screen.

Register 16 Ć

CRC Errors

The SCC performs an errorĆchecking routine called a

Cyclic Redundancy Check (CRC) as a result of the SDLC

protocol. Any message received that is flagged with a

CRC error is ignored and no reply is transmitted. This

results in a reĆtransmission of the message. The value in

this register will increment if a CRC error occurs. This

value should ideally remain zero.

Register 17 Ć

Overrun Errors

The value in this register will increment if the buffer in the

SCC is filled and no read of the data has occurred. This

value should ideally remain zero.

Register 18 Ć

Abort Errors

The abort sequence feature of the SDLC protocol is not

used in the transmission routine. Therefore, if an abort is

detected in a receiver, there has been error. The value in

this register will increment with each abort error detected.

This value should ideally remain zero.