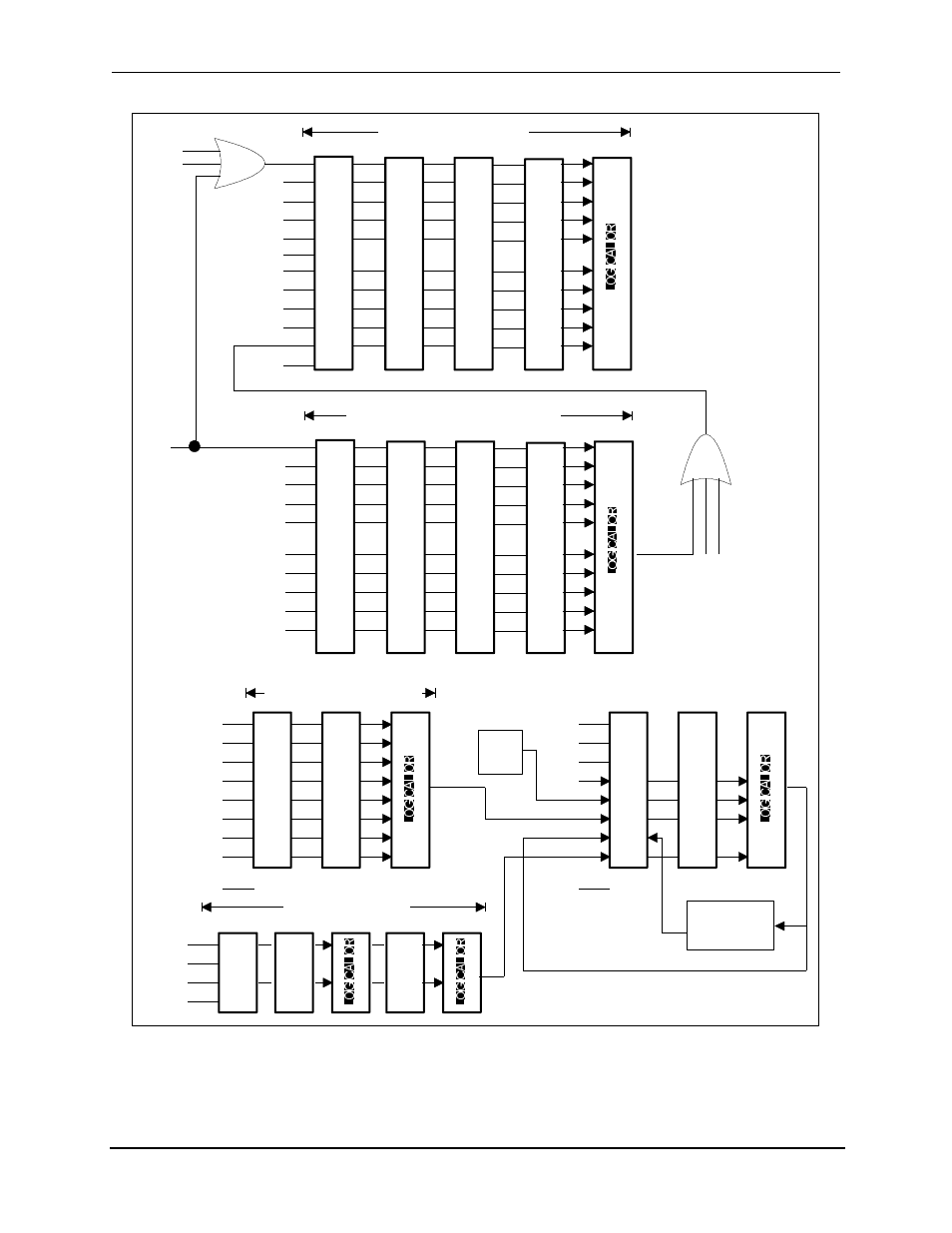

Programming manual lx \ ls series ii 151, Figure 7-1: status register model – AMETEK Lx Series II Programming Manual User Manual

Page 155

Programming Manual

Lx \ Ls Series II

151

1

2

4

8

16

512

1024

2048

4096

8192

1

2

4

8

16

512

1024

2048

4096

8192

1

2

4

8

16

512

1024

2048

4096

8192

1

2

4

8

16

512

1024

2048

4096

8192

QUESTIONABLE STATUS

CONDITION

PTR/NTR

EVENT

ENABLE

OV

OCP

SOA

UNR

OT

n.u.

RI

CL peak

Rail

CL rms

n.u.

1

2

4

8

16

512

1024

2048

4096

8192

1

2

4

8

16

512

1024

2048

4096

8192

1

2

4

8

16

512

1024

2048

4096

8192

1

2

4

8

16

512

1024

2048

4096

8192

QUESTIONABLE INSTRUMENT ISUMMARY

CONDITION

PTR/NTR

EVENT

ENABLE

(1 identical register set for each phase)

OCP

SOA

UNR

OT

n.u.

RI

CL peak

Rail

CL rms

n.u.

0

1

2

3

4

5-8

9

10

11

12

13

14,15

0

1

2

3

4

5-8

9

10

11

12

13-15

Isum

ø3

ø2

ø1

OV

ø1 ø2 ø3

EVENT

ENABLE

OPC

n.u.

OYE

DDE

EXE

CME

n.u.

PON

0

1

2

3

4

5

6

7

1

4

8

16

32

128

1

4

8

16

32

128

STANDARD EVENT STATUS

STATUS

BYTE

SERVICE

REQUEST

ENABLE

n.u.

n.u.

n.u.

QUES

MAV

ESB

MSS

OPER

0

1

2

3

4

5

6

7

8

16

32

64

128

8

16

32

128

SERVICE

REQUEST

GENERATION

DATA

DATA

DATA

OUTPUT

QUEUE

RQS

CAL

n.u.

WTG

n.u.

0

1-4

5

6-15

1

32

OPERATION STATUS

1

32

1

32

CONDITION PTR/NTR EVENT ENABLE

Figure 7-1: Status Register Model.