AMETEK Lx Series II Programming Manual User Manual

Page 104

Programming Manual

Lx \ Ls Series II

100

If the same bits in both NTR and PTR registers are set to 1, then any transition of that bit at

the Operation Condition register sets the corresponding bit in the Operation Event register.

If the same bits in both NTR and PTR registers are set to 0, then no transition of that bit at the

Operation Condition register can set the corresponding bit in the Operation Event register.

Note: Setting a bit in the PTR or NTR filter can of itself generate positive or negative events in

the corresponding Operation Event register.

Command Syntax

STATus:OPERation:NTRansition

STATus:OPERation:PTRansition

Parameters

0 to 32727

Default Value

0

Examples

STAT:OPER:NTR 32

STAT:OPER:PTR 1

Query Syntax

STATus:OPERation:NTR?

STATus:OPERation:PTR?

Returned Parameters

Related Commands

STAT:OPER:ENAB

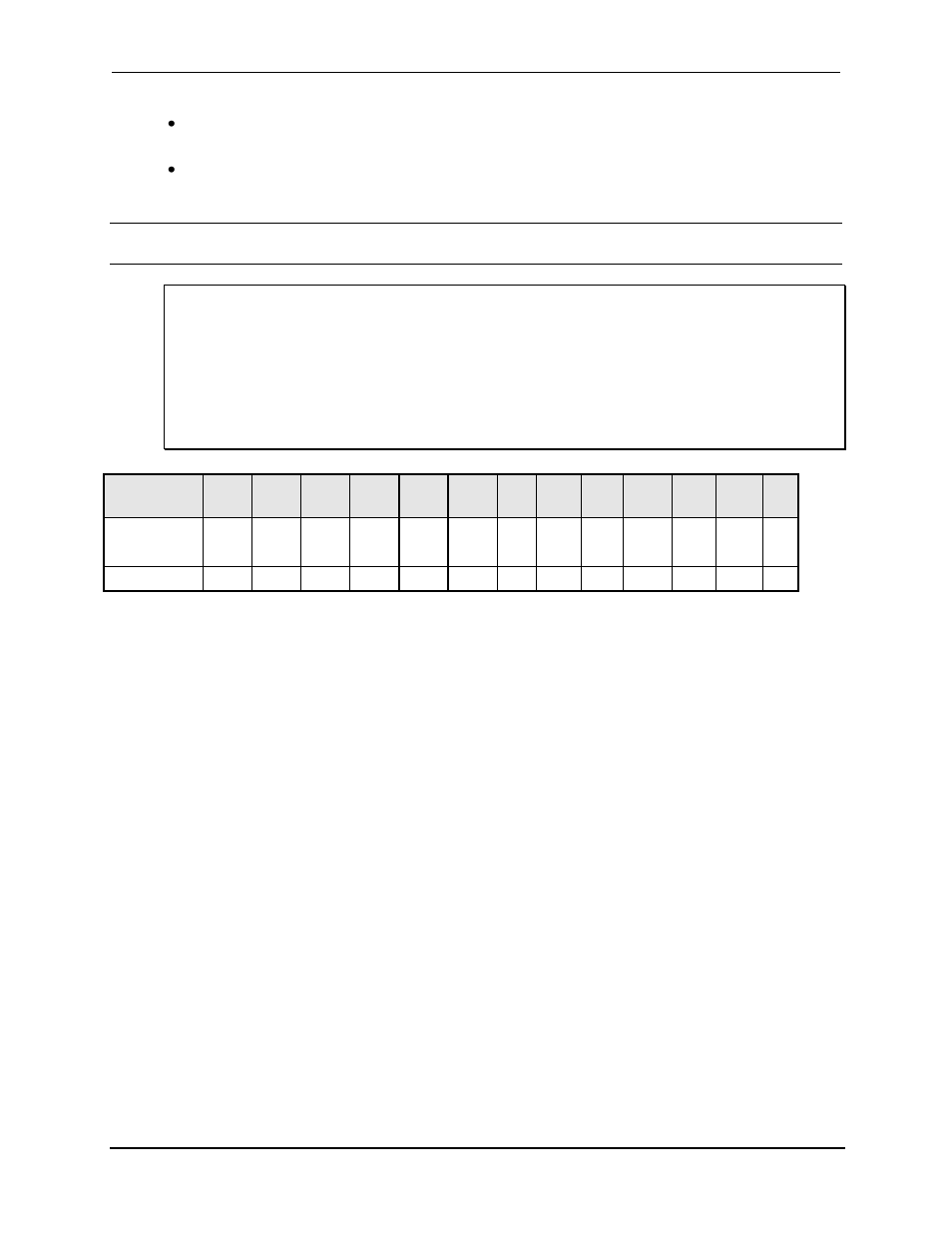

Bit

Position

15

14

13

12

11

10

9

8-5

4

3

2

1

0

Bit Name

not

used

not

used

Isum

CL

rms

Rail

not

used

RI

not

used

TO

UNR

not

use

d

OCP

OV

Bit Weight

8192

4096

2048

512

16

8

2

1

Table 4-4: Bit Configuration of Questionable Registers

OV

over-voltage protection has tripped

OCP

over-current protection has tripped

UNR

output is unregulated

TO

over-temperature protection has tripped

RI

remote inhibit is active

Rail

loss of input phase detected

CL rms

rms current limit is active

Isum

summary of Isum registers

STATus:QUEStionable?

This query returns the value of the Questionable Event register. The Event register is a read-only

register which holds (latches) all events that are passed by the Questionable NTR and/or PTR

filter. Reading the Questionable Event register clears it.

On the Lx\Ls Series, each signal that is fed into the Questionable Status Condition register is

logically-ORed from three corresponding status signals that originate from each phase.