7 test interface, Table 3.16 jtag, ice, and debug pins, Test interface – Avago Technologies LSI53C1030 User Manual

Page 77: Jtag, ice, and debug pins, Section 3.7, “test interface

Test Interface

3-17

Version 2.2

Copyright © 2001, 2002, 2003 by LSI Logic Corporation. All rights reserved.

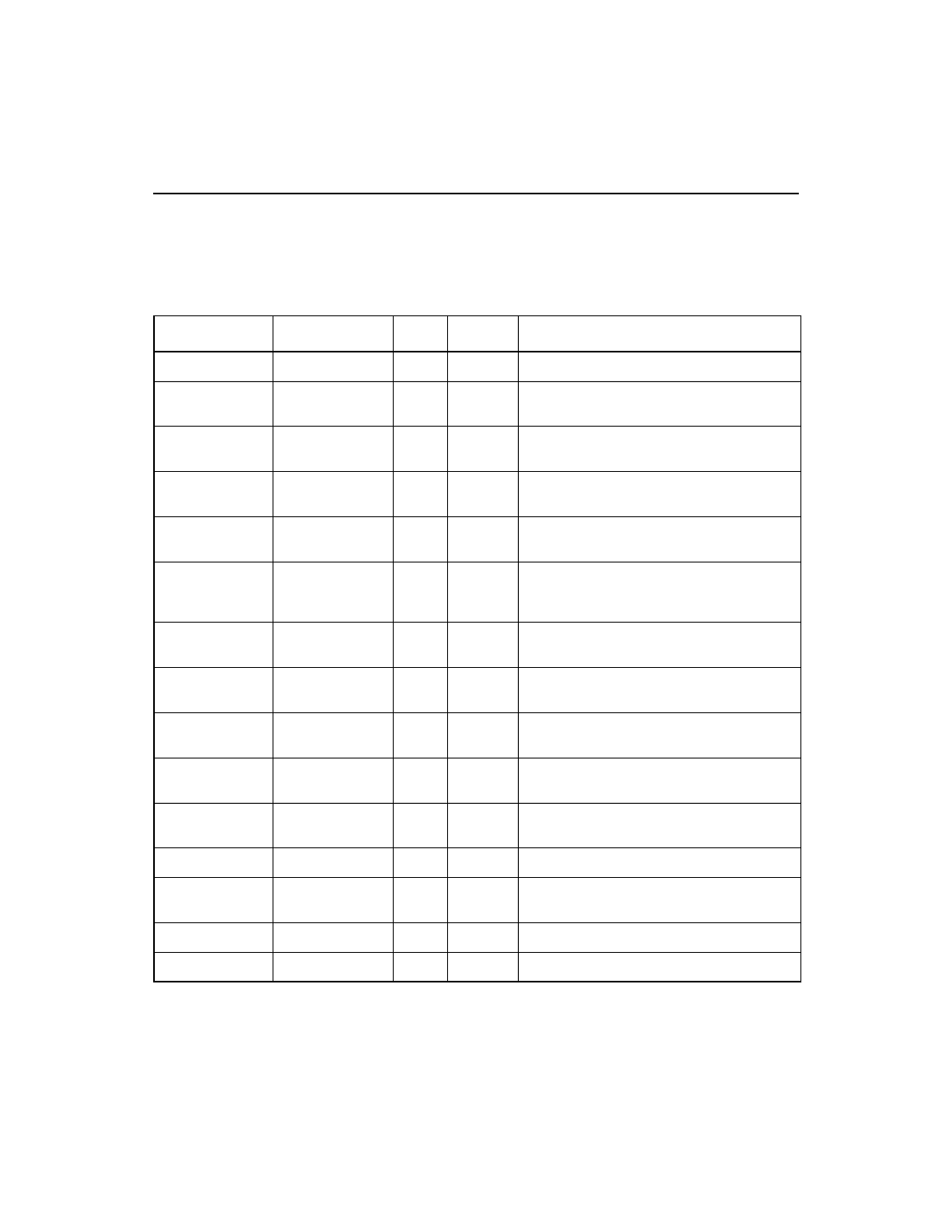

3.7 Test Interface

describes the JTAG and ICE debug signals.

Table 3.16

JTAG, ICE, and Debug Pins

Signal Name

BGA Position

Type

Strength Description

TST_RST/

AD5

I

N/A

Active low Test Reset is for test purposes.

TCK_CHIP

AC6

I

N/A

Chip Test Clock provides a JTAG test

clock signal.

TDI_CHIP

AF3

I

N/A

Chip Test Data In provides the JTAG test

data in signal.

TDO_CHIP

AD6

O

8 mA

Chip Test Data Out provides the JTAG test

data out signal.

TMS_CHIP

AE4

I

N/A

Chip Test Mode Select provides the JTAG

test mode select signal.

RTCK_ICE

AA5

O

8 mA

Test Clock Acknowledge provides the

JTAG test clock acknowledge signal for the

In-Circuit Emulator (ICE) debug logic.

TRST_ICE/

AB4

I

N/A

Test Reset provides the JTAG test reset

signal for the ICE debug logic.

TCK_ICE

AA4

I

N/A

Test Clock provides the JTAG test clock

signal for the ICE debug logic.

TDI_ICE

AB3

I

N/A

Test Data In provides the JTAG test data in

signal for the ICE debug logic.

TDO_ICE

AD2

O

8 mA

Test Data Out provides the JTAG test data

out signal for the ICE debug logic.

TMS_ICE

Y5

I

N/A

Test Mode Select provides the test mode

select signal for the ICE debug logic.

TRACECLK

B3

O

8 mA

Reserved.

TRACEPKT[7:0]

F4, G5, E3, C2,

E4, F5, B2, D4

O

8 mA

Reserved.

TRACESYNC

E5

O

8 mA

Reserved.

PIPESTAT[2:0]

C3, E6, D5

O

8 mA

Reserved.