Avago Technologies LSI53C1030 User Manual

Page 5

Preface

v

Version 2.2

Copyright © 2001, 2002, 2003 by LSI Logic Corporation. All rights reserved.

PCI Special Interest Group

2575 N. E. Katherine

Hillsboro, OR 97214

(800) 433-5177; (503) 693-6232 (International); FAX (503) 693-8344

Conventions Used in This Manual

The first time a word or phrase is defined in this manual, it is italicized.

The word assert means to drive a signal true or active. The word

deassert means to drive a signal false or inactive. Signals that are active

LOW end with a “/.”

Hexadecimal numbers are indicated by the prefix “0x” —for example,

0x32CF. Binary numbers are indicated by the prefix “0b” —for example,

0b0011.0010.1100.1111.

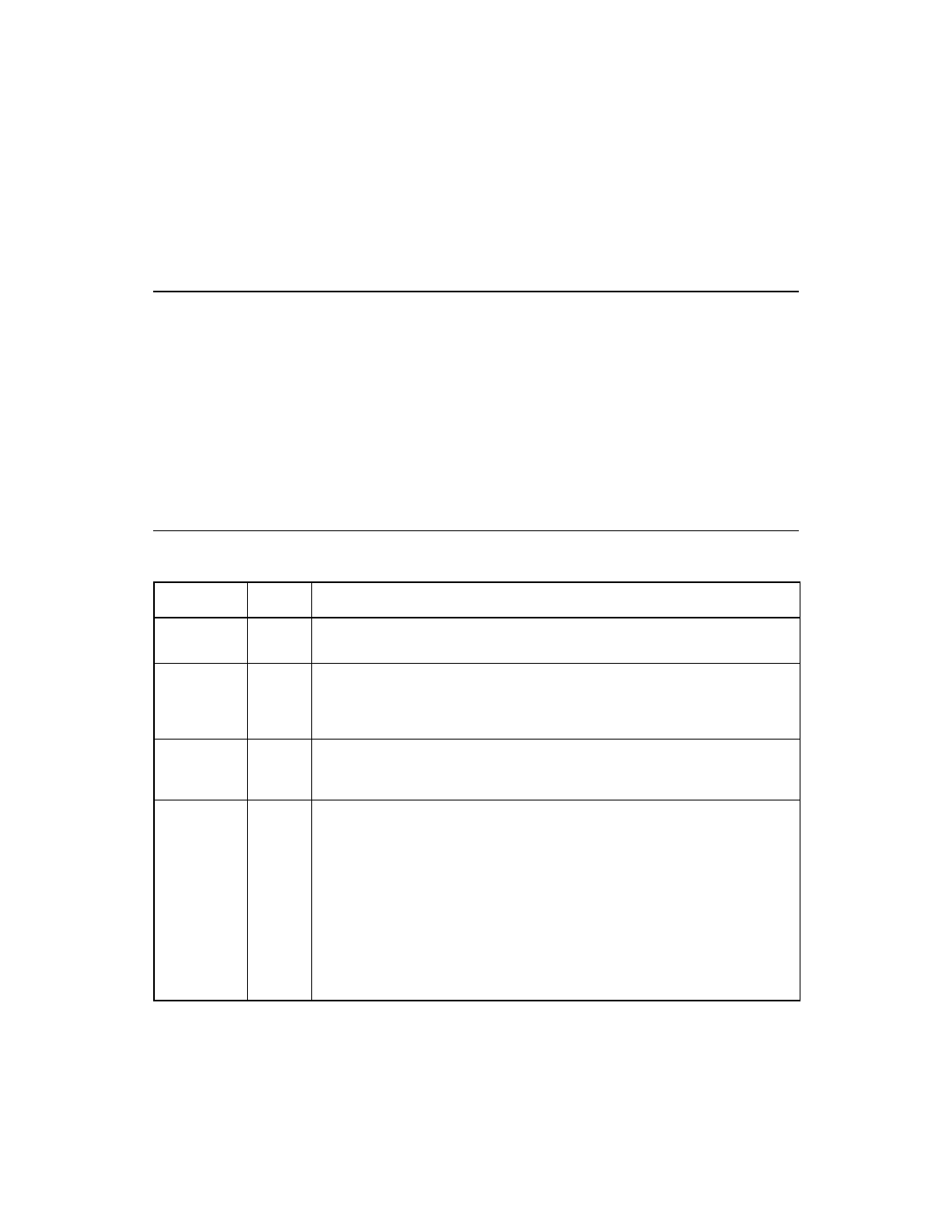

Revision History

Revision

Date

Remarks

Version 2.2

9/2003

Corrected SCSI clock period and LOW/HIGH times in Table 5.13.

Updated references to Integrated RAID (IR).

Version 2.1

6/2003

Updated the external memory timing diagrams.

Updated the default Subsystem ID value.

Updated the ZCR behavior description.

Updated the Multi-ICE test interface description.

Version 2.0

4/2002

Added register summary appendix.

Updated the electrical characteristics.

Updated the Index.

Preliminary

Version 1.0

12/2001

Updated the description of Fusion-MPT architecture in Chapter 1.

Updated External Memory Interface descriptions in Chapter 2.

Added Test Interface description to Chapter 2.

Added Zero Channel RAID interface description to Chapters 2 and 3.

Updated the MAD Power-On Sense pin description in Chapter 3.

Updated signal descriptions and lists to include the ZCR-related pins.

Updated electrical and environmental characteristics in Chapter 5.

Removed figures relating to SE SCSI electrical and timing characteristics

from Chapter 5.

Removed SCSI timing information from Chapter 5 and referred readers to

the SCSI specification.

Removed PSBRAM interface and all related information.