Avago Technologies LSI53C1030 User Manual

Page 75

Memory Interface

3-15

Version 2.2

Copyright © 2001, 2002, 2003 by LSI Logic Corporation. All rights reserved.

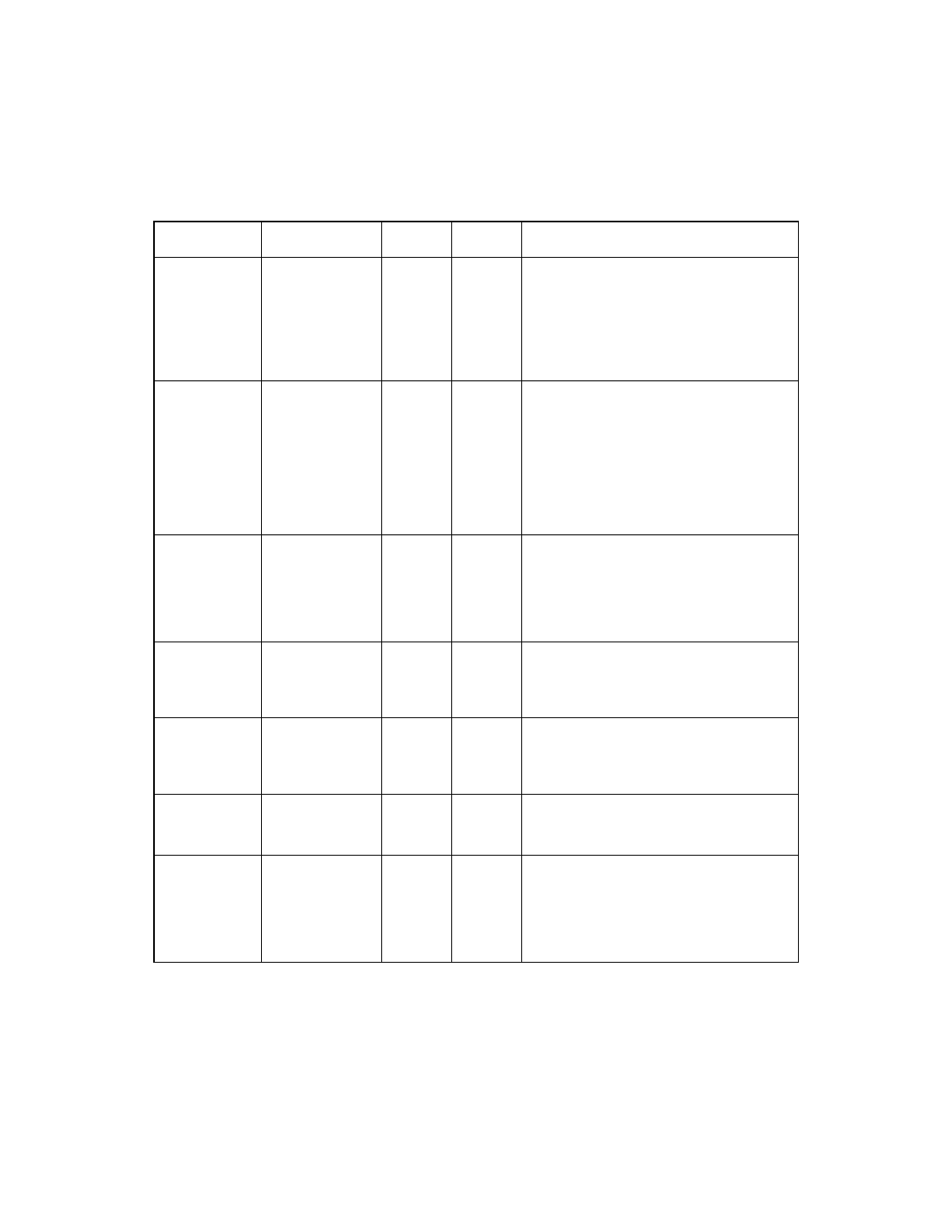

MAD[15:0]

D22, E21, B25,

D23, E22, C24,

F22, E23, D26,

E25, H22, F24,

G23, D25, F23,

G22

I/O

8 mA

The Memory Address and Data Bus

carries the memory and address signals

for the Flash ROM and NVSRAM

interfaces on MAD[7:0]. These pins also

provide the Power-On Sense options that

configure operating parameters during

chip power up or reset.

MADP[1:0]

C22, B24

I/O

8 mA

The Memory Address and Data Parity

signals provide parity checking for

MAD[15:0]. By default, the LSI53C1030

uses even parity. The user can enable odd

parity through the Fusion-MPT

architecture. These pins also provide the

Power-On Sense options that configure

operating parameters during chip power

up or reset.

MOE/

G26

O

4 mA

The LSI53C1030 asserts active LOW

Memory Output Enable to indicate that

the selected NVSRAM or Flash ROM

device can drive data. This signal is

typically an asynchronous input to

NVSRAM and/or Flash ROM devices.

BWE[1:0]/

E24, H23

O

8 mA

The LSI53C1030 asserts active LOW

Memory Byte Write Enables to allow

single byte writes to the NVSRAM. BWE0/

enables writes on MAD[7:0].

RAMCE/

D20

O

8 mA

When MAD[3] is pulled HIGH, the

LSI53C1030 asserts active LOW

synchronous RAM Chip Enable to select

the NVSRAM.

FLSHCE/

G25

O

8 mA

The LSI53C1030 asserts active LOW

Flash Chip Enable to enable data

transfers with a single 8-bit device.

FLSHALE[1:0]/

J24, K22

O

8 mA

The Flash ROM and NVSRAM interfaces

use active LOW Flash Address Latch

Enable. For the Flash ROM, these signals

provide clocks for address latches. For the

NVSRAM, these signals provide the

memory address strobe.

Table 3.13

Flash ROM/NVSRAM Interface Pins (Cont.)

Signal Name

BGA Position

Type

Strength Description