Figure5.11 flash rom write cycle, Flash rom write cycle, Flash rom write cycle (cont.) – Avago Technologies LSI53C1030 User Manual

Page 141

External Memory Timing Diagrams

5-17

Version 2.2

Copyright © 2001, 2002, 2003 by LSI Logic Corporation. All rights reserved.

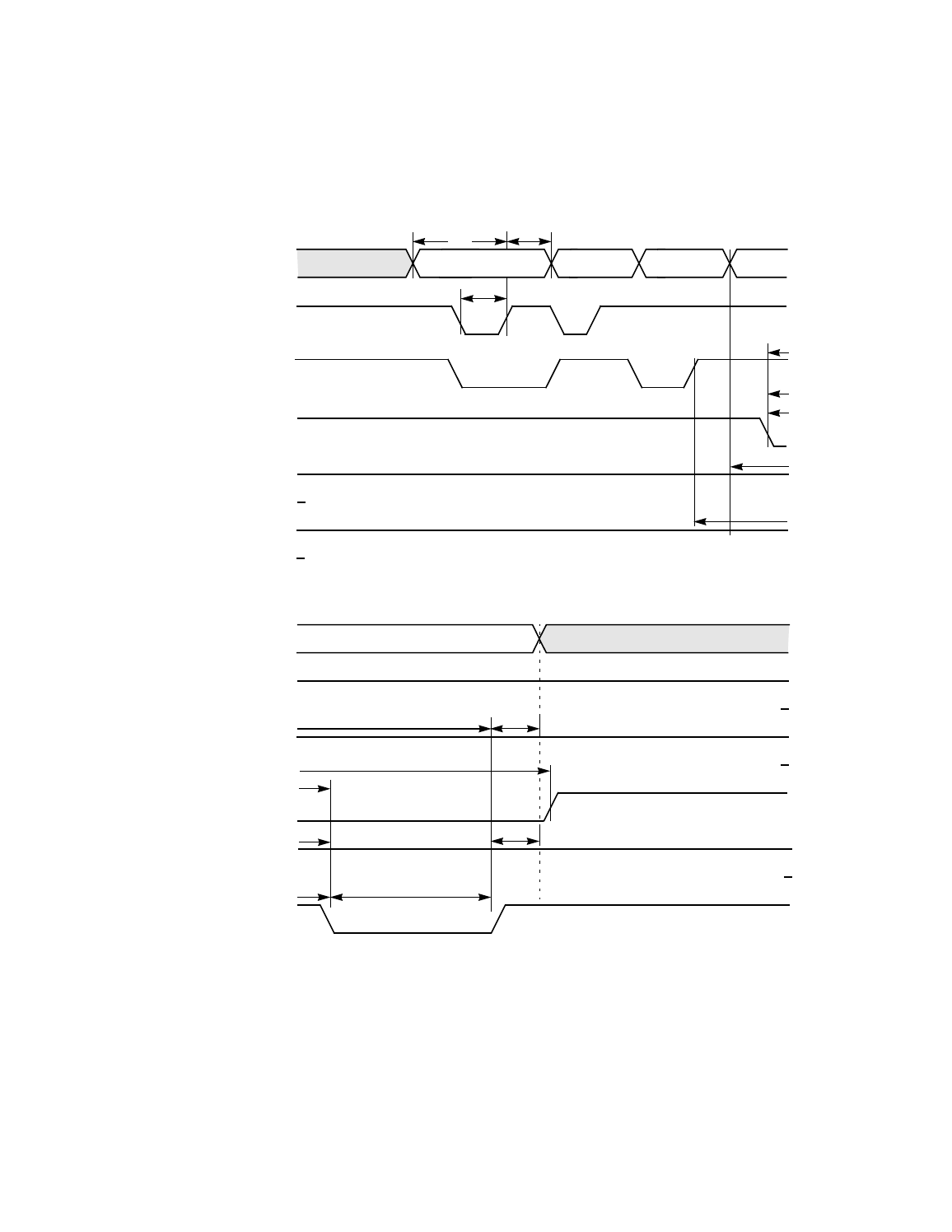

Figure 5.11 Flash ROM Write Cycle

Figure 5.11 Flash ROM Write Cycle (Cont.)

MAD Bus

(Driven by LSI53C1030)

High Order Address

Middle Order

Address

Low Order

Address

FLSHALE1/

(Driven by LSI53C1030)

FLSHALE0/

(Driven by LSI53C1030)

FLSHCE/

(Driven by LSI53C1030)

MOE/

(Driven by LSI53C1030)

BWE0/

(Driven by LSI53C1030)

t

13

t

11

t

12

t

24

t

25

Write

Data

Valid

t

23

t

20

t

27

MAD Bus

(Driven by LSI53C1030)

FLSHALE1/

(Driven by LSI53C1030)

FLSHALE0/

(Driven by LSI53C1030)

FLSHCE/

(Driven by LSI53C1030)

MOE/

(Driven by LSI53C1030)

BWE0/

(Driven by LSI53C1030)

t

24

t

25

t

21

Valid Write Data

t

20

t

23

t

22

t

26

t

27

See also other documents in the category Avago Technologies Hardware:

- MGA-725M4 (4 pages)

- MGA-71543 (4 pages)

- MGA-71543 (3 pages)

- MGA-82563 (6 pages)

- 3ware SAS 9750-8i (48 pages)

- 3ware 9690SA-8I (Channel) (138 pages)

- 3ware 9690SA-8I (Channel) (380 pages)

- 3ware SAS 9750-8i (29 pages)

- 3ware 9550SXU-8LP (Channel) (149 pages)

- 3ware 9550SXU-8LP (Channel) (40 pages)

- 3ware 9650SE-8LPML (Channel) (45 pages)

- 3ware 9690SA-8I (Channel) (27 pages)

- 3ware 9690SA-8I (Channel) (361 pages)

- 6160 SAS Switch (2 pages)

- MegaRAID SAS 9380-8e (43 pages)

- Cache Protection for RAID Controller Cards (139 pages)

- Cache Protection for RAID Controller Cards (13 pages)

- MegaRAID SAS 9271-8iCC (13 pages)

- MegaRAID SAS 9361-8i (13 pages)

- MegaRAID SAS 9266-8i (12 pages)

- MegaRAID SAS 9266-8i (20 pages)

- MegaRAID SAS 9271-8iCC (26 pages)

- MegaRAID SafeStore Software (502 pages)

- MegaRAID SAS 9285-8ecv (80 pages)

- MegaRAID SAS 9285-8ecv (92 pages)

- MegaRAID SAS 0260CV-4i (49 pages)

- MegaRAID SAS 9271-8i (8 pages)

- MegaRAID SAS 0260CV-4i (72 pages)

- MegaRAID SAS 0260CV-4i (64 pages)

- MegaRAID SAS 9361-8i (7 pages)

- MegaRAID SAS 9341-8i (8 pages)

- MegaRAID SAS 9380-4i4e (7 pages)

- MegaRAID SAS 9380-8e (7 pages)

- MegaRAID SAS 0260CV-4i (28 pages)

- MegaRAID SAS 9240-8i (4 pages)

- MegaRAID SAS 9280-24i4e (14 pages)

- MegaRAID SAS 9280-24i4e (16 pages)

- MegaRAID SAS 9260-16i (12 pages)

- MegaRAID SafeStore Software (8 pages)

- MegaRAID SAS 9280-8e (22 pages)

- MegaRAID SAS 9260-8i (4 pages)

- MegaRAID SAS 9261-8i (4 pages)

- MegaRAID SAS 9285-8e (12 pages)

- MegaRAID SAS 9280-16i4e (12 pages)

- MegaRAID SAS 9280-4i4e (4 pages)