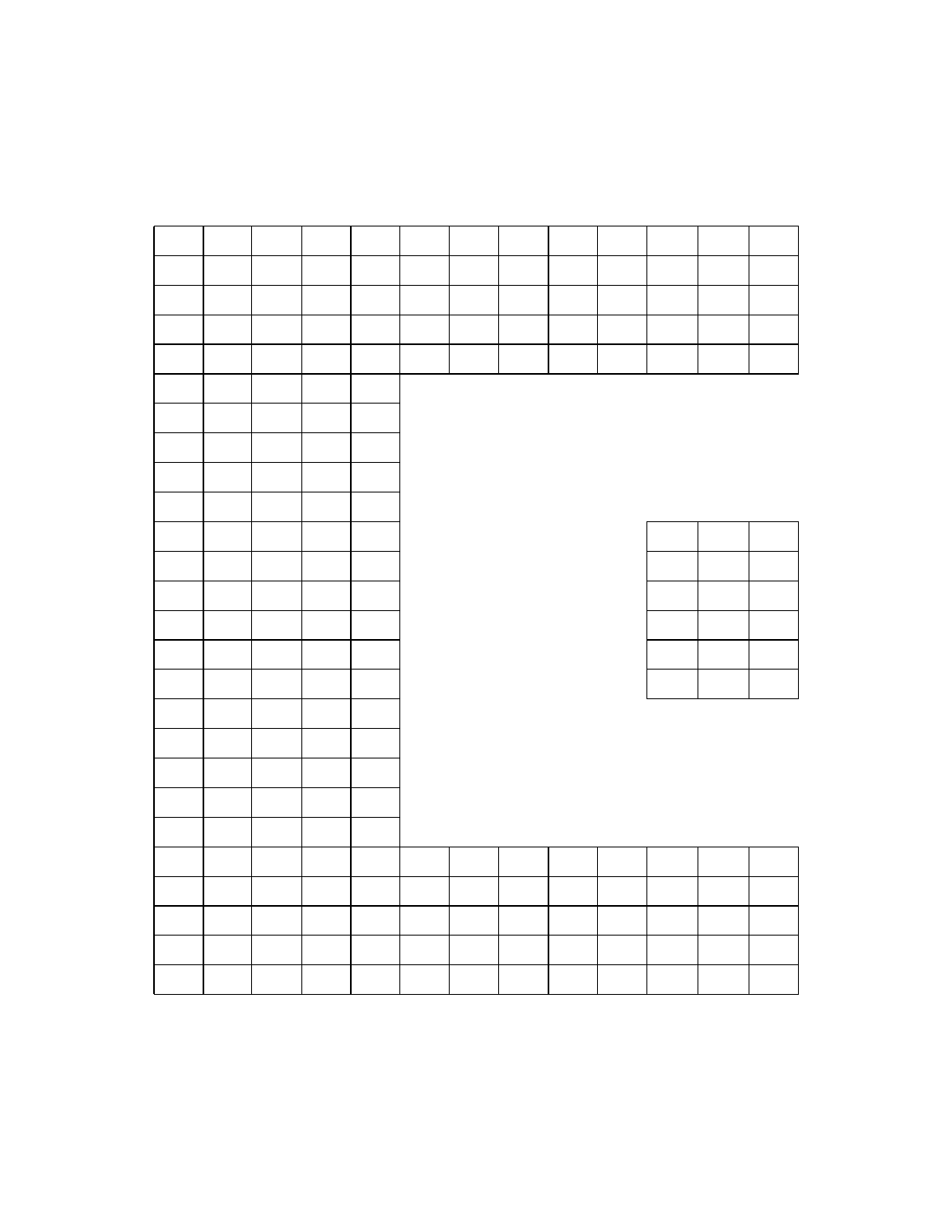

Figure5.12 lsi53c1030 456-pin bga top view, Lsi53c1030 456-pin bga top view, Figure 5.12 – Avago Technologies LSI53C1030 User Manual

Page 144: 20 specifications

5-20

Specifications

Version 2.2

Copyright © 2001, 2002, 2003 by LSI Logic Corporation. All rights reserved.

Figure 5.12 LSI53C1030 456-Pin BGA Top View

A1

A2

A3

A4

A5

A6

A7

A8

A9

A10

A11

A12

A13

VDD_IO

VDD_IO

B_SD12

−

B_SD12+

VSS_IO

VDD_IO

B_SDP1

−

B_SD0+

VSS_IO

VDD_IO

B_RBIAS

B_SD6

−

VSS_IO

B1

B2

B3

B4

B5

B6

B7

B8

B9

B10

B11

B12

B13

VSS_IO

TRACE

PKT1

TRACECLK

VSSC

B_SD13+

B_SD14+

B_SD15+

B_SD0

−

B_SD1+

B_SD4

−

B_SD5

−

B_SD6+

B_VDDBIAS

C1

C2

C3

C4

C5

C6

C7

C8

C9

C10

C11

C12

C13

VDDA

TRACE

PKT4

PIPESTAT2

VSS_IO

TN

B_SD13

−

VDD_IO

VSS_IO

B_SD2

−

B_SD4+

VDD_IO

VSS_IO

B_SDP0+

D1

D2

D3

D4

D5

D6

D7

D8

D9

D10

D11

D12

D13

A_SD11+

VDDC

VDD_IO

TRACE

PKT0

PIPESTAT0

VDDC

TESTCLKEN

B_SD15

−

B_SD1

−

B_SD3

−

B_SD5+

B_SDP0

−

B_SATN+

E1

E2

E3

E4

E5

E6

E7

E8

E9

E10

E11

E12

E13

VSS_IO

A_

DIFFSENS

TRACE

PKT5

TRACE

PKT3

TRACSYNC

PIPESTAT1 SCANMODE

B_SD14

−

B_SDP1+

B_SD2+

B_SD3+

B_SD7+

B_SD7

−

F1

F2

F3

F4

F5

VDD_IO

A_SD11-

SCLK

TRACE

PKT7

TRACE

PKT2

G1

G2

G3

G4

G5

A_SD10+

A_SD10

−

VSS_IO

VSSC

TRACE

PKT6

H1

H2

H3

H4

H5

A_SD8-

A_SD8+

VDD_IO

A_SD9+

VSSA

J1

J2

J3

J4

J5

VSS_IO

A_SREQ-

A_SREQ+

A_SD9-

A_SIO+

K1

K2

K3

K4

K5

VDD_IO

A_SSEL+

A_SCD-

A_SCD+

A_SIO-

L1

L2

L3

L4

L5

L11

L12

L13

A_SMSG+

A_SMSG-

VSS_IO

A_SSEL

−

A_SACK+

VSS_IO

VSS_IO

VSS_IO

M1

M2

M3

M4

M5

M11

M12

M13

A_SRST

−

A_SRST+

VDD_IO

A_SATN

−

A_SACK

−

VSS_IO

VSS_IO

VSS_IO

N1

N2

N3

N4

N5

N11

N12

N13

VSS_IO

VDDC

A_SBSY

−

A_SBSY+

A_SATN+

VSS_IO

VSS_IO

VSS_IO

P1

P2

P3

P4

P5

P11

P12

P13

VDD_IO

VSSC

A_SD7+

A_SDP0

−

A_SDP0+

VSS_IO

VSS_IO

VSS_IO

R1

R2

R3

R4

R5

R11

R12

R13

A_RBIAS

A_SD5+

VSS_IO

A_SD7

−

A_SD6+

VSS_IO

VSS_IO

VSS_IO

T1

T2

T3

T4

T5

T11

T12

T13

A_VDDBIAS

A_SD5

−

VDD_IO

A_SD4+

A_SD6

−

VSS_IO

VSS_IO

VSS_IO

U1

U2

U3

U4

U5

VSS_IO

A_SD4

−

A_SD2+

A_SD3+

A_SD3

−

V1

V2

V3

V4

V5

VDD_IO

A_SD2

−

A_SD0+

A_SD1

−

A_SD1+

W1

W2

W3

W4

W5

A_SDP1+

A_SDP1

−

VSS_IO

A_SD0

−

ASD15+

Y1

Y2

Y3

Y4

Y5

A_SD15

−

A_SD14+

VDD_IO

IDDTN

TMS_ICE

AA1

AA2

AA3

AA4

AA5

VSS_IO

A_SD14

−

A_SD13+

TCK_ICE

RTCK_ICE

AB1

AB2

AB3

AB4

AB5

AB6

AB7

AB8

AB9

AB10

AB11

AB12

AB13

VDD_IO

A_SD13

−

TDI_ICE

TRST_ICE/

VSSC

TESTACLK

VSSC

VSSC

ALT_INTB/

RST/

AD28

AD24

C_BE3/

AC1

AC2

AC3

AC4

AC5

AC6

AC7

AC8

AC9

AC10

AC11

AC12

AC13

A_SD12+

CLK

MODE_1

VSS_IO

DIS_SCSI_

FSN/

IOPD_GNT/

TCK_CHIP

VDDC

INTA/

NC

PCI5VBIAS

AD27

AD23

IDSEL

AD1

AD2

AD3

AD4

AD5

AD6

AD7

AD8

AD9

AD10

AD11

AD12

AD13

A_SD12

−

TDO_ICE

VDDC

VDD_IO

TST_RST/

TDO_CHIP

VSS_IO

VDD_IO

PCI5VBIAS

REQ/

VSS_IO

VDD_IO

AD22

AE1

AE2

AE3

AE4

AE5

AE6

AE7

AE8

AE9

AE10

AE11

AE12

AE13

VSS_IO

TESTHCLK

VDDC

TMS_CHIP

PVT1

PCI5VBIAS

INTB/

GNT/

AD31

AD29

AD26

AD25

AD21

AF1

AF2

AF3

AF4

AF5

AF6

AF7

AF8

AF9

AF10

AF11

AF12

AF13

VDD_IO

VSS_IO

TDI_CHIP

PVT2

VDD_IO

VSS_IO

ALT_INTA/

AD30

VDD_IO

VSS_IO

AD20

PCI5VBIAS

VDD_IO