Intel IA-32 User Manual

Page 82

3-2 Vol. 3A

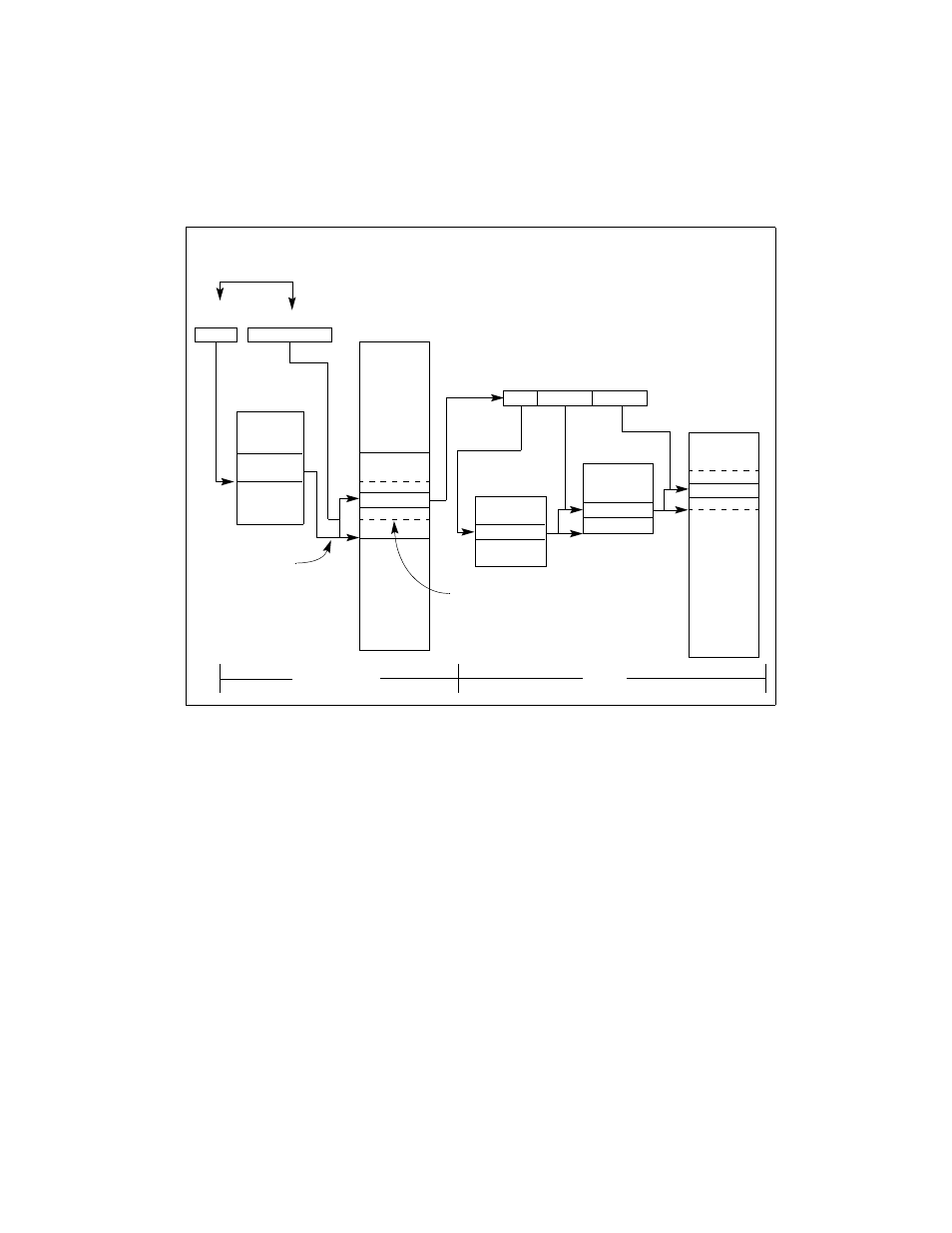

PROTECTED-MODE MEMORY MANAGEMENT

If paging is not used, the linear address space of the processor is mapped directly into the phys-

ical address space of processor. The physical address space is defined as the range of addresses

that the processor can generate on its address bus.

Because multitasking computing systems commonly define a linear address space much larger

than it is economically feasible to contain all at once in physical memory, some method of

“virtualizing” the linear address space is needed. This virtualization of the linear address space

is handled through the processor’s paging mechanism.

Paging supports a “virtual memory” environment where a large linear address space is simulated

with a small amount of physical memory (RAM and ROM) and some disk storage. When using

paging, each segment is divided into pages (typically 4 KBytes each in size), which are stored

either in physical memory or on the disk. The operating system or executive maintains a page

directory and a set of page tables to keep track of the pages. When a program (or task) attempts

to access an address location in the linear address space, the processor uses the page directory

and page tables to translate the linear address into a physical address and then performs the

requested operation (read or write) on the memory location.

Figure 3-1. Segmentation and Paging

Global Descriptor

Table (GDT)

Linear Address

Space

Segment

Segment

Descriptor

Offset

Logical Address

Segment

Base Address

Page

Phy. Addr.

Lin. Addr.

Segment

Selector

Dir

Table

Offset

Linear Address

Page Table

Page Directory

Entry

Physical

Space

Entry

(or Far Pointer)

Paging

Segmentation

Address

Page