3 ia32_mcg_status msr, D (see section 14.3.1.3, “ia32_mcg_status msr, Section 14.3.1.3, “ia32_mcg_status msr”) – Intel IA-32 User Manual

Page 530

14-4 Vol. 3A

MACHINE-CHECK ARCHITECTURE

Where:

•

Count field, bits 0 through 7 — Indicates the number of hardware unit error-reporting

banks available in a particular processor implementation.

•

MCG_CTL_P (register present) flag, bit 8 — Indicates that the MCG_CTL register is

present when set and absent when clear.

Bits 9 through 63 are reserved. The effect of writing to the MCG_CAP register is undefined.

14.3.1.3

IA32_MCG_STATUS MSR

The IA32_MCG_STATUS MSR (called the MCG_STATUS MSR for P6 family processors)

describes the current state of the processor after a machine-check exception has occurred (see

Figure 14-4).

Where:

•

RIPV (restart IP valid) flag, bit 0 — Indicates (when set) that program execution can be

restarted reliably at the instruction pointed to by the instruction pointer pushed on the stack

when the machine-check exception is generated. When clear, the program cannot be

reliably restarted at the pushed instruction pointer.

•

EIPV (error IP valid) flag, bit 1 — Indicates (when set) that the instruction pointed to by

the instruction pointer pushed onto the stack when the machine-check exception is

generated is directly associated with the error. When this flag is cleared, the instruction

pointed to may not be associated with the error.

•

MCIP (machine check in progress) flag, bit 2 — Indicates (when set) that a machine-

check exception was generated. Software can set or clear this flag. The occurrence of a

second Machine-Check Event while MCIP is set will cause the processor to enter a

shutdown state. For information on processor behavior in the shutdown state, please refer

to the description in Chapter 5, “Interrupt and Exception Handling”: “Interrupt 8—Double

Fault Exception (#DF)”.

Bits 63-03 in IA32_MCG_STATUS are reserved.

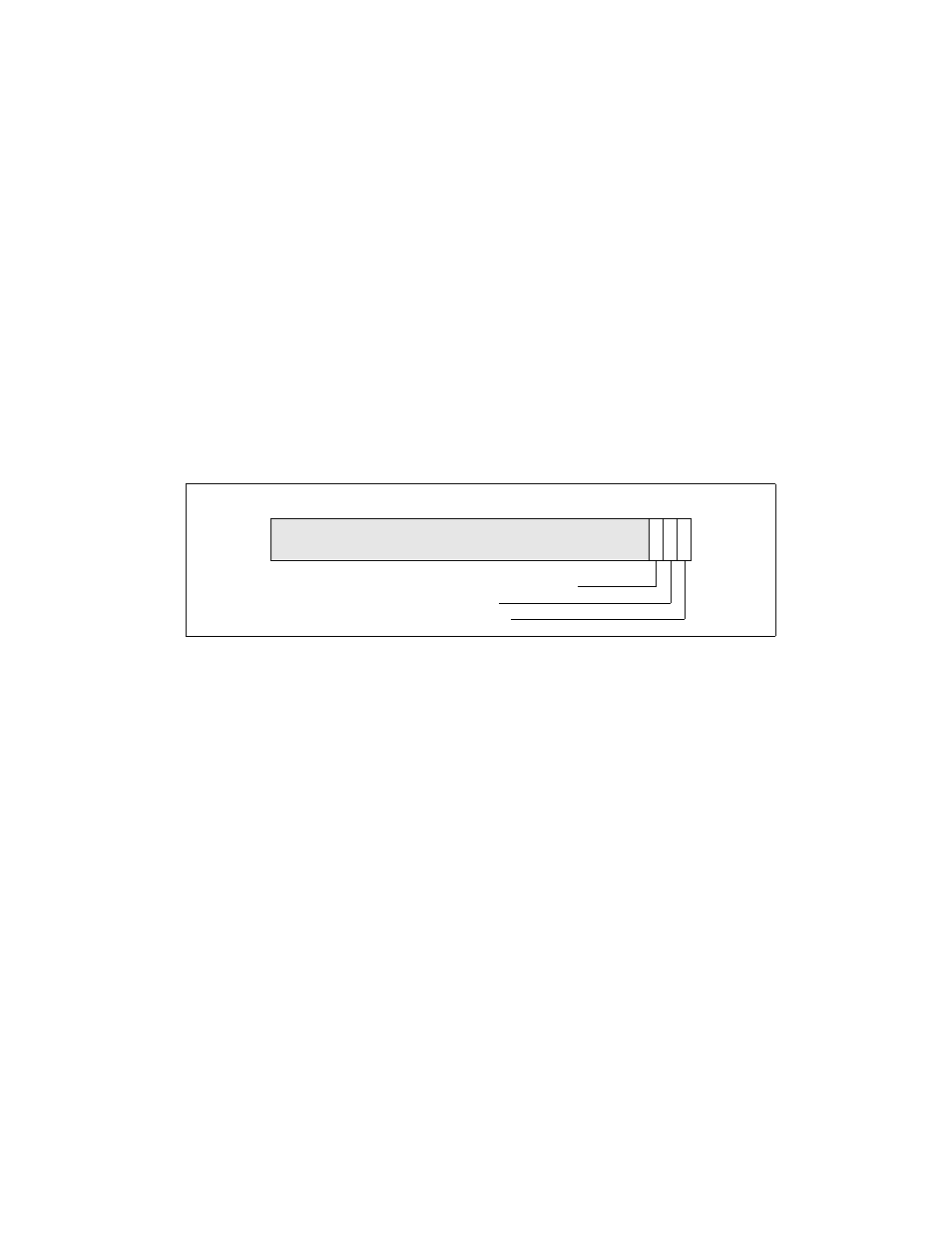

Figure 14-4. IA32_MCG_STATUS Register

EIPV—Error IP valid flag

MCIP—Machine check in progress flag

63

0

Reserved

1

2

3

E

I

P

V

M

C

I

P

R

I

P

V

RIPV—Restart IP valid flag