Intel IA-32 User Manual

Page 118

3-38 Vol. 3A

PROTECTED-MODE MEMORY MANAGEMENT

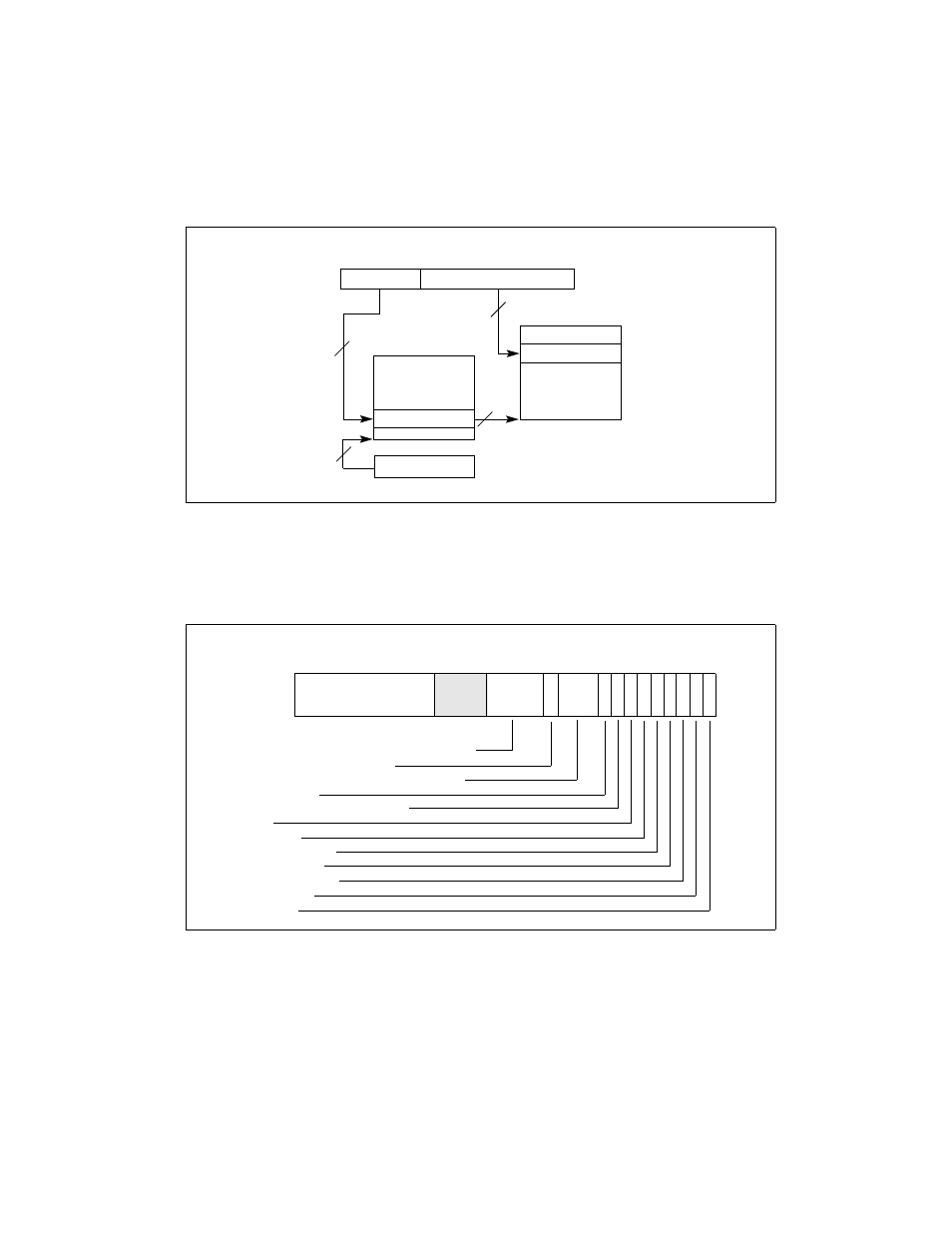

Figure 3-23 shows the format for the page-directory entries when 4-MByte pages and 36-bit

physical addresses are being used. Section 3.7.6, “Page-Directory and Page-Table Entries”

describes the functions of the flags and fields in bits 0 through 11.

Figure 3-22. Linear Address Translation (4-MByte Pages)

Figure 3-23. Format of Page-Directory Entries for 4-MByte Pages and

36-Bit Physical Addresses

0

Directory

Offset

Page Directory

Directory Entry

CR3 (PDBR)

4-MByte Page

Physical Address

31

21

22

Linear Address

1024 PDE = 1024 Pages

10

22

32*

*32 bits aligned onto a 4-KByte boundary.

14

31

Available for system programmer’s use

Global page

Page size (must be set to 1)

Dirty

12 11

9 8 7 6 5 4 3 2 1 0

P

S

P

C

A

D

Accessed

Cache disabled

Write-through

User/Supervisor

Read/Write

Present

D

P

P

W

T

U

/

S

R

/

W

G

Avail.

Page Base Address

Page-Directory Entry (4-MByte Page)

22 21

Reserved

13

16

(Bits 22 Through 31)

Page Base Address (Bits 32 Through 35)

Page Attribute Table Index

17

P

A

T