2 identifying logical processors in an mp system, See figure 7-5) – Intel IA-32 User Manual

Page 304

7-36 Vol. 3A

MULTIPLE-PROCESSOR MANAGEMENT

The value of valid APIC_IDs need not be contiguous across package boundary or core bound-

aries.

7.10.2

Identifying Logical Processors in an MP System

For any IA-32 processor, system hardware establishes an initial APIC ID that is unique for each

logical processor following power-up or RESET (see Section 7.7.1). Each logical processor on

the system is allocated an initial APIC ID. BIOS may implement features that tell the OS to

support less than the total number of logical processors on the system bus. Those logical proces-

sors that are not available to applications at runtime are halted during the OS boot process. As a

result, the number valid local APIC_IDs that can be queried by affinitizing-current-thread-

context (See Example 7-3) is limited to the number of logical processors enabled at runtime by

the OS boot process.

Table 7-1 shows the APIC IDs that are initially reported for logical processors in a system with

four MP-type Intel Xeon processors (a total of 8 logical processors, each physical package has

one processor core and supports Hyper-Threading Technology). Of the two logical processors

within a Intel Xeon processor MP, logical processor 0 is designated the primary logical

processor and logical processor 1 as the secondary logical processor.

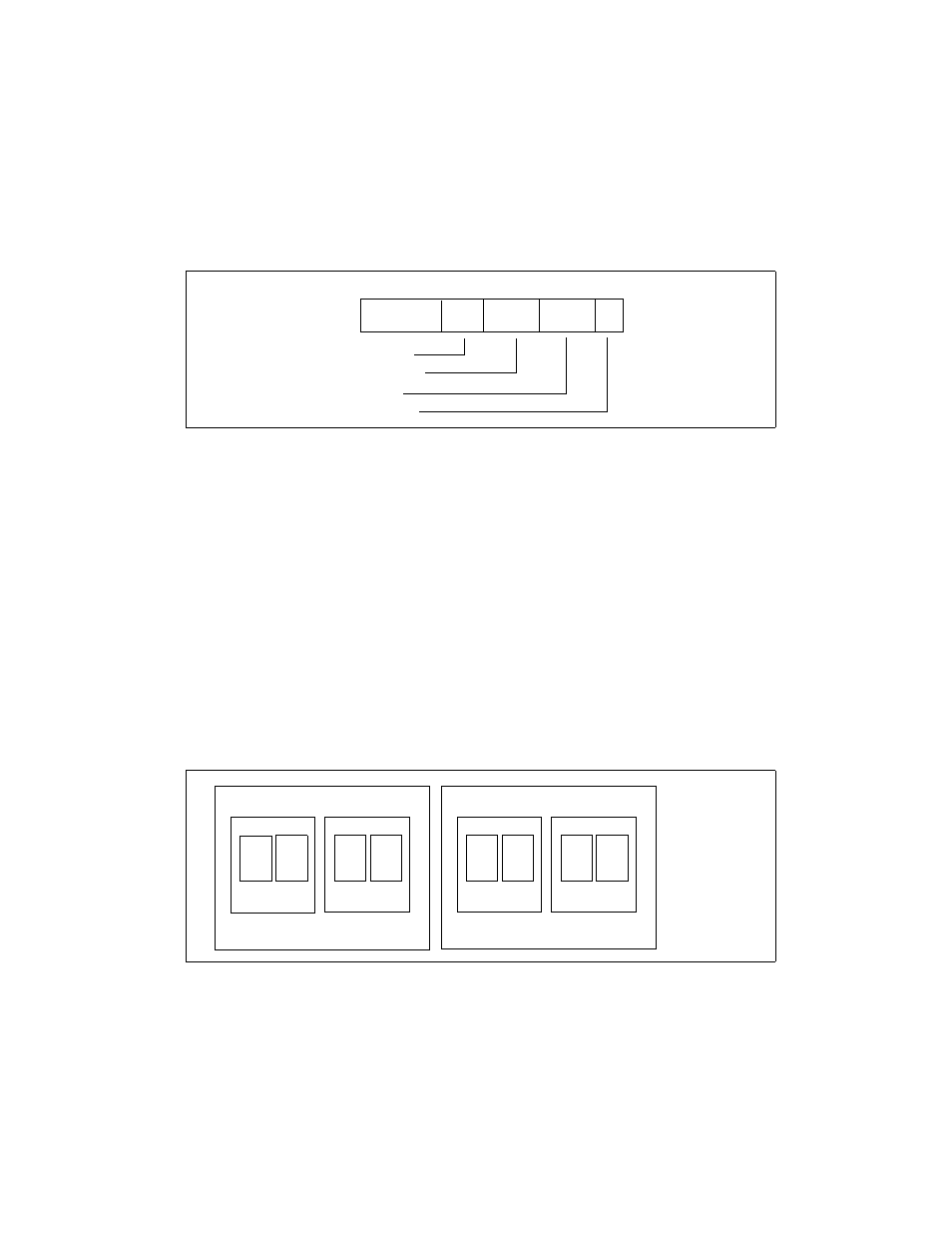

Figure 7-5. Generalized Four level Interpretation of the initial APIC ID

Figure 7-6. Topological Relationships between Hierarchical IDs in a Hypothetical MP

Platform

0

Package ID

SMT ID

7

Cluster ID

Reserved

Core ID

Package 0

Core 0

T0

T1

Core1

T0

T1

Package 1

Core 0

T0

T1

Core1

T0

T1

SMT_ID

Core ID

Package ID