1 task and processor priorities, E tpr (see figure 8-18), the irr – Intel IA-32 User Manual

Page 361

Vol. 3A 8-37

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

8.8.3.1

Task and Processor Priorities

The local APIC also defines a task priority and a processor priority that it uses in determining

the order in which interrupts should be handled. The task priority is a software selected value

between 0 and 15 (see Figure 8-18) that is written into the task priority register (TPR). The TPR

is a read/write register.

NOTE

In this discussion, the term “task” refers to a software defined task, process,

thread, program, or routine that is dispatched to run on the processor by the

operating system. It does not refer an IA-32 architecture defined task as

described in Chapter 6, “Task Management.”

The task priority allows software to set a priority threshold for interrupting the processor. The

processor will service only those interrupts that have a priority higher than that specified in the

TPR. If software sets the task priority in the TPR to 0, the processor will handle all interrupts; it

is it set to 15, all interrupts are inhibited from being handled, except those delivered with the

NMI, SMI, INIT, ExtINT, INIT-deassert, and start-up delivery mode. This mechanism enables

the operating system to temporarily block specific interrupts (generally low priority interrupts)

from disturbing high-priority work that the processor is doing.

Note that the task priority is also used to determine the arbitration priority of the local processor

(see Section 8.6.2.4, “Lowest Priority Delivery Mode”).

The processor priority is set by the processor, also to value between 0 and 15 (see Figure 8-19)

that is written into the processor priority register (PPR). The PPR is a read only register. The

processor priority represents the current priority at which the processor is executing. It is used

to determine whether a pending interrupt can be dispensed to the processor.

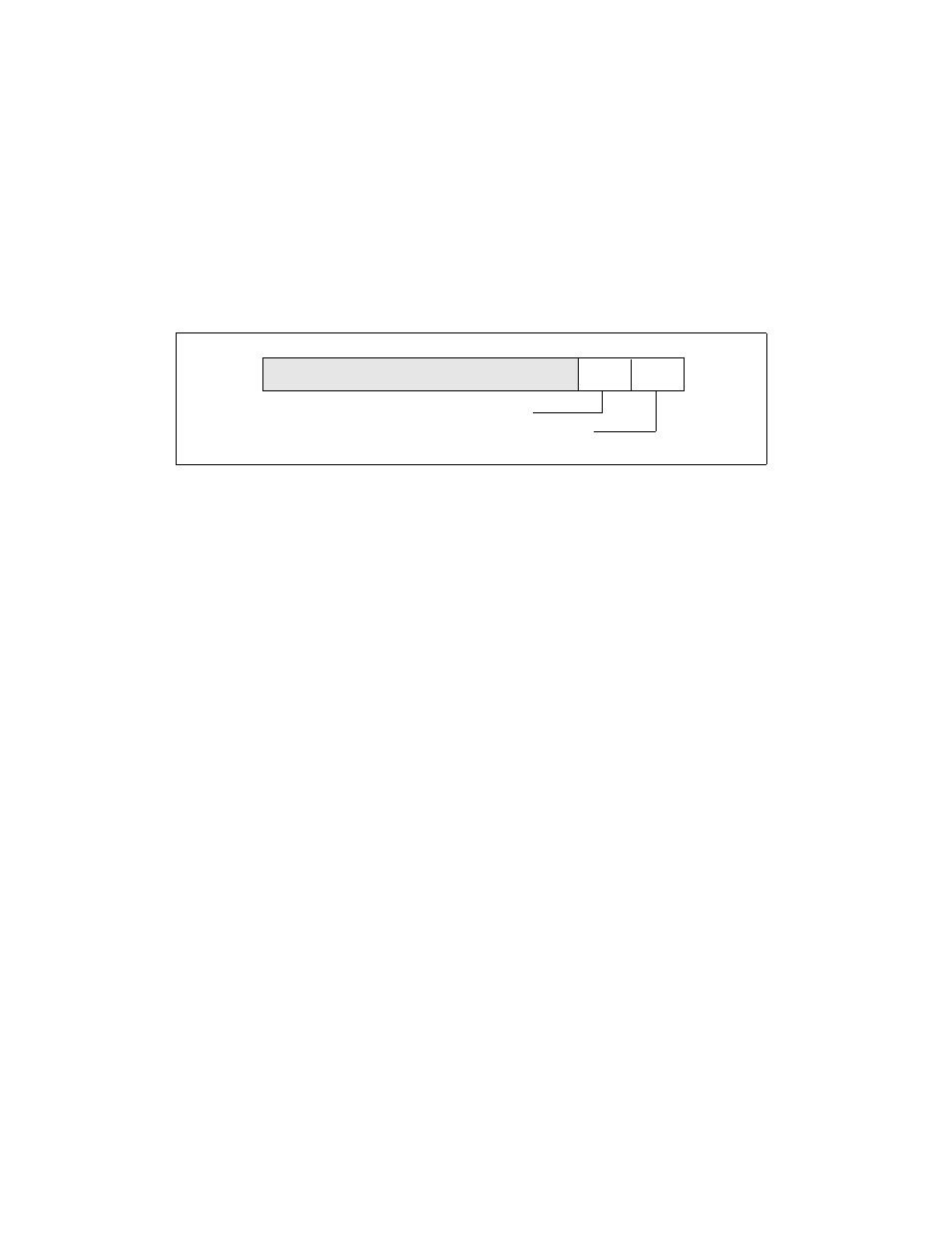

Figure 8-18. Task Priority Register (TPR)

31

0

7

8

Reserved

Address: FEE0 0080H

Value after reset: 0H

Task Priority Sub-Class

Task Priority

4 3