Table 3-3, 1 linear address translation (4-kbyte pages) – Intel IA-32 User Manual

Page 103

Vol. 3A 3-23

PROTECTED-MODE MEMORY MANAGEMENT

3.7.1

Linear Address Translation (4-KByte Pages)

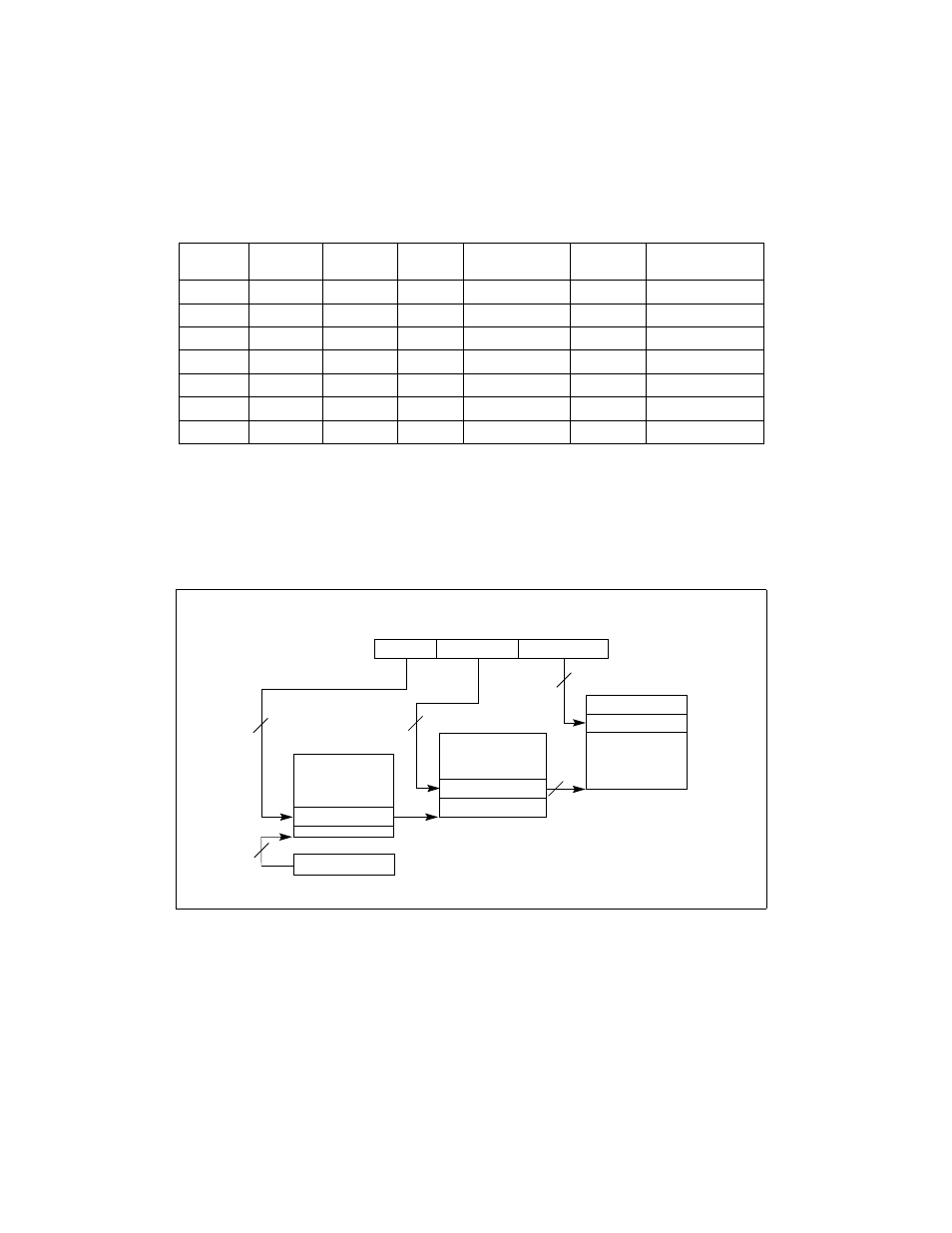

Figure 3-12 shows the page directory and page-table hierarchy when mapping linear addresses

to 4-KByte pages. The entries in the page directory point to page tables, and the entries in a page

table point to pages in physical memory. This paging method can be used to address up to 2

20

pages, which spans a linear address space of 2

32

bytes (4 GBytes).

Table 3-3. Page Sizes and Physical Address Sizes

PG Flag,

CR0

PAE Flag,

CR4

PSE Flag,

CR4

PS Flag,

PDE

PSE-36 CPUID

Feature Flag

Page Size

Physical Address

Size

0

X

X

X

X

—

Paging Disabled

1

0

0

X

X

4 KBytes

32 Bits

1

0

1

0

X

4 KBytes

32 Bits

1

0

1

1

0

4 MBytes

32 Bits

1

0

1

1

1

4 MBytes

36 Bits

1

1

X

0

X

4 KBytes

36 Bits

1

1

X

1

X

2 MBytes

36 Bits

Figure 3-12. Linear Address Translation (4-KByte Pages)

0

Directory

Table

Offset

Page Directory

Directory Entry

CR3 (PDBR)

Page Table

Page-Table Entry

4-KByte Page

Physical Address

31

21

11

12

22

Linear Address

1024 PDE

∗ 1024 PTE = 2

20

Pages

32*

10

12

10

*32 bits aligned onto a 4-KByte boundary.

20