Intel IA-32 User Manual

Page 507

Vol. 3A 12-9

SSE, SSE2 AND SSE3 SYSTEM PROGRAMMING

On a task switch, the operating system task switching code must execute the following pseudo-

code to set the TS flag according to the current owner of the x87 FPU/MMX/SSE/SSE2/SSE3

state. If the new task (task B in this example) is not the current owner of this state, the TS flag

is set to 1; otherwise, it is set to 0.

IF Task_Being_Switched_To

≠ x87FPU_MMX_SSE_SSE2_SSE3_StateOwner

THEN

CR0.TS

← 1;

ELSE

CR0.TS

← 0;

FI;

If a new task attempts to access an x87 FPU, MMX, XMM, or MXCSR register while the TS

flag is set to 1, a device-not-available exception (#NM) is generated. The device-not-available

exception handler executes the following pseudo-code.

FSAVE “To x87FPU/MMX/SSE/SSE2/SSE3 State Save Area for Current

x87FPU_MMX_SSE_SSE2_SSE3_StateOwner”;

FRSTOR “x87FPU/MMX/SSE/SSE2/SSE3 State From Current Task’s

x87FPU/MMX/SSE/SSE2/SSE3 State Save Area”;

x87FPU_MMX_SSE_SSE2_SSE3_StateOwner

← Current_Task;

CR0.TS

← 0;

This exception handler code performs the following tasks:

•

Saves the x87 FPU, MMX, XMM, or MXCSR registers in the state save area for the

current owner of the x87 FPU/MMX/SSE/SSE2/SSE3 state.

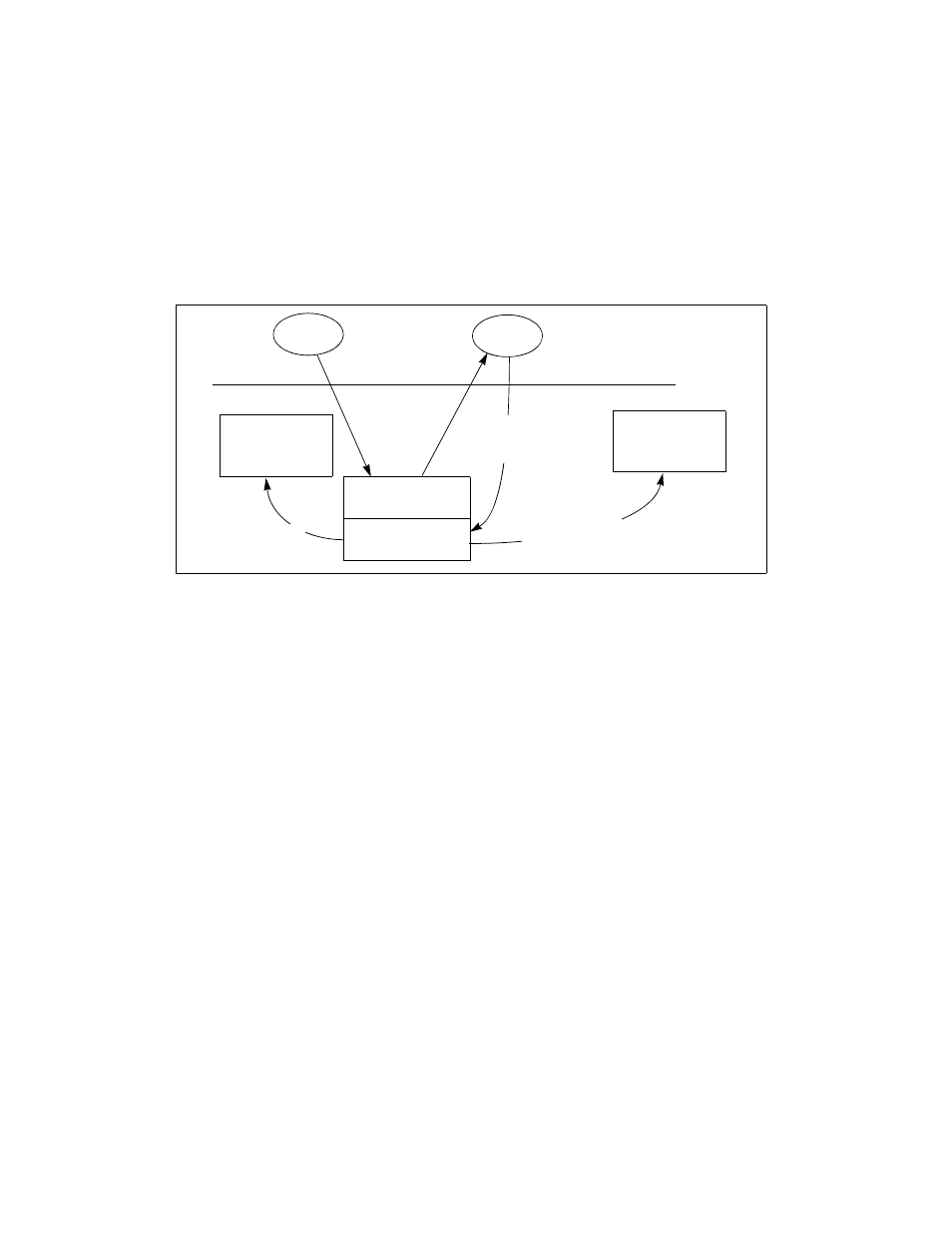

Figure 12-1. Example of Saving the x87 FPU, MMX, SSE, and SSE2 State During an

Operating-System Controlled Task Switch

Task A

Task B

Application

Operating System

Task A

Operating System

Task Switching Code

Device-Not-Available

Exception Handler

Owner of x87 FPU,

CR0.TS=1 and x87 FPU

MMX, SSE, SSE2 or SSE3

Instruction is encountered

MMX, SSE, SSE2,

x87 FPU/MMX/

State Save Area

SSE/SSE2/SSE3

Task B

x87 FPU/MMX/

State Save Area

SSE/SSE2/SSE3

Saves Task A

x87 FPU/MMX/

SSE/SSE2/SSE3 State

Loads Task B

x87 FPU/MMX/

SSE/SSE2/SSE3 State

SSE3 State