4 thermal monitoring and protection – Intel IA-32 User Manual

Page 515

Vol. 3A 13-5

POWER AND THERMAL MANAGEMENT

13.4

THERMAL MONITORING AND PROTECTION

The IA-32 architecture provides the following mechanisms for monitoring temperature and

controlling thermal power:

1.

The catastrophic shutdown detector forces processor execution to stop if the processor’s

core temperature rises above a preset limit.

2.

Automatic thermal monitoring mechanism forces the processor to reduce it’s power

consumption in order to maintain a predetermined temperature limit.

3.

The software controlled clock modulation mechanism permits operating systems to

implement power management policies that reduce power consumption; this is in addition

to the reduction offered by automatic thermal monitoring mechanisms.

4.

On-die digital thermal sensor and interrupt mechanisms permit the OS to manage

thermal conditions natively without relying on BIOS or other system board components.

The first mechanism is not visible to software. The other three mechanisms are visible to soft-

ware using processor feature information returned by executing CPUID with EAX = 1.

The second mechanism, automatic thermal monitoring, provides two modes of operation. One

mode modulates the clock duty cycle; the second mode changes the processor’s frequency. Both

modes are used to control the core temperature of the processor.

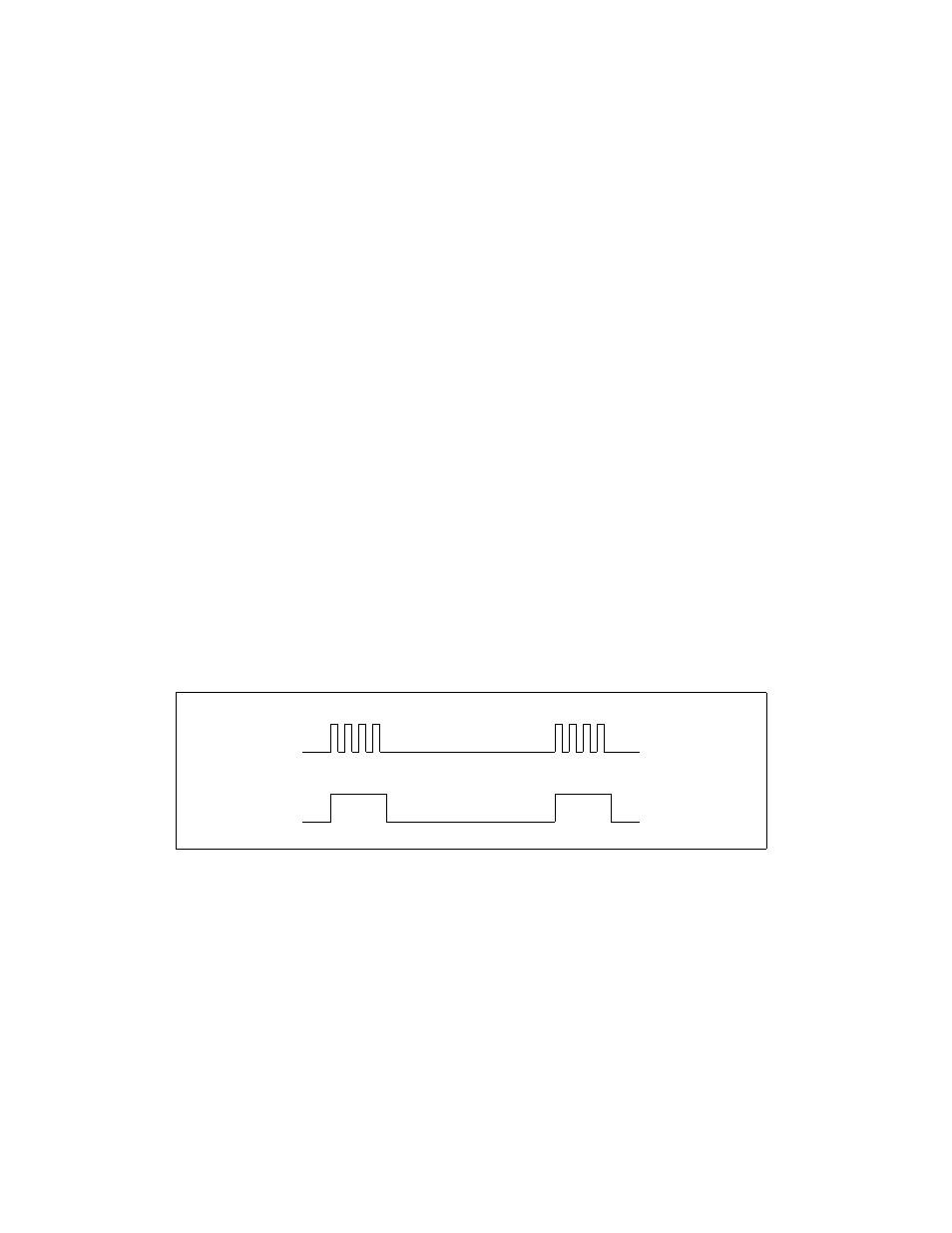

The third mechanism modulates the clock duty cycle of the processor. As shown in Figure 13-2,

the phrase ‘duty cycle’ does not refer to the actual duty cycle of the clock signal. Instead it refers

to the time period during which the clock signal is allowed to drive the processor chip. By using

the stop clock mechanism to control how often the processor is clocked, processor power

consumption can be modulated.

For previous automatic thermal monitoring mechanisms, software controlled mechanisms that

changed processor operating parameters to impact changes in thermal conditions. Software did

not have native access to the native thermal condition of the processor; nor could software alter

the trigger condition that initiated software program control.

The fourth mechanism (listed above) provides access to an on-die digital thermal sensor using

a model-specific register and uses an interrupt mechanism to alert software to initiate digital

thermal monitoring.

Figure 13-2. Processor Modulation Through Stop-Clock Mechanism

Clock Applied to Processor

Stop-Clock Duty Cycle

25% Duty Cycle (example only)