Set. table 4-6 – Intel IA-32 User Manual

Page 172

4-42 Vol. 3A

PROTECTION

tures. Execute-disable bit protection can be activated using the execute-disable bit at any level

of the paging structure, irrespective of the corresponding entry in other levels. When execute-

disable-bit protection is not activated, the page can be used as code or data.

In legacy PAE-enabled mode, Table 4-7 and Table 4-8 show the effect of setting the execute-

disable bit for code and data pages.

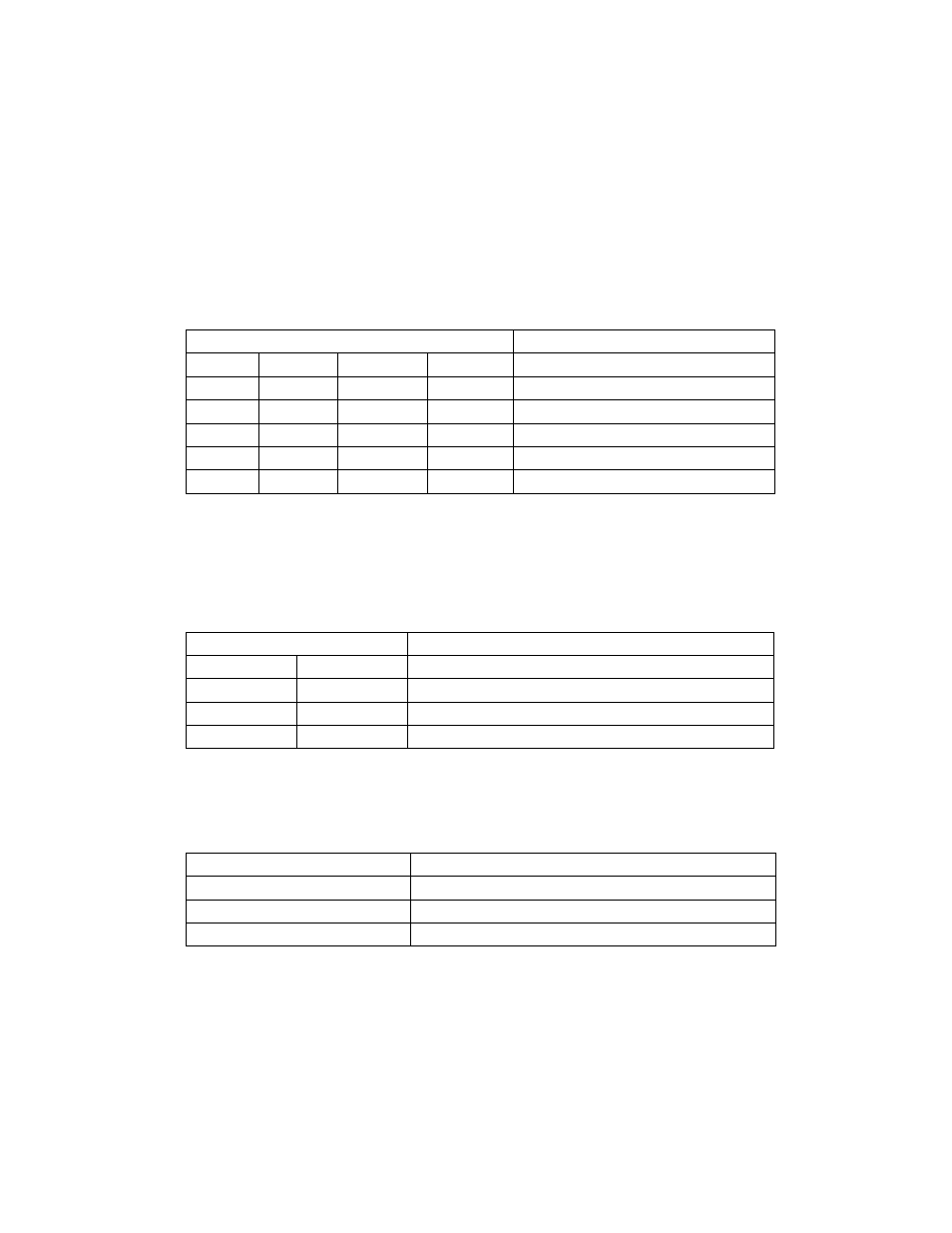

Table 4-6. IA-32e Mode Page Level Protection Matrix

with Execute-Disable Bit Capability

Execute Disable Bit Value (Bit 63)

Valid Usage

PML4

PDP

PDE

PTE

Bit 63 = 1

*

*

*

Data

*

Bit 63 = 1

*

*

Data

*

*

Bit 63 = 1

*

Data

*

*

*

Bit 63 = 1

Data

Bit 63 = 0

Bit 63 = 0

Bit 63 = 0

Bit 63 = 0

Data/Code

NOTE:

* Value not checked.

Table 4-7. Legacy PAE-Enabled 4-KByte Page Level Protection Matrix

with Execute-Disable Bit Capability

Execute Disable Bit Value (Bit 63)

Valid Usage

PDE

PTE

Bit 63 = 1

*

Data

*

Bit 63 = 1

Data

Bit 63 = 0

Bit 63 = 0

Data/Code

NOTE:

* Value not checked.

Table 4-8. Legacy PAE-Enabled 2-MByte Page Level Protection

with Execute-Disable Bit Capability

Execute Disable Bit Value (Bit 63)

Valid Usage

PDE

Bit 63 = 1

Data

Bit 63 = 0

Data/Code