3 machine-check error codes interpretation, 7 guidelines for writing machine-check software – Intel IA-32 User Manual

Page 543

Vol. 3A 14-17

MACHINE-CHECK ARCHITECTURE

14.6.3

Machine-Check Error Codes Interpretation

Appendix E, “Interpreting Machine-Check Error Codes,” provides information on interpreting

the MCA error code, model-specific error code, and other information error code fields. For

P6 family processors, information has been included on decoding external bus errors. For

Pentium 4 and Intel Xeon processors; information is included on external bus, internal timer

and memory hierarchy errors.

14.7

GUIDELINES FOR WRITING MACHINE-CHECK SOFTWARE

The machine-check architecture and error logging can be used in two different ways:

•

To detect machine errors during normal instruction execution, using the machine-check

exception (#MC).

•

To periodically check and log machine errors.

To use the machine-check exception, the operating system or executive software must provide

a machine-check exception handler. This handler can be designed specifically for Pentium 4 and

Intel Xeon processors or for P6 family processors. It can also be a portable handler that handles

processor machine-check errors from several generations of IA-32 processors.

A special program or utility is required to log machine errors.

Guidelines for writing a machine-check exception handler or a machine-error logging utility are

given in the following sections.

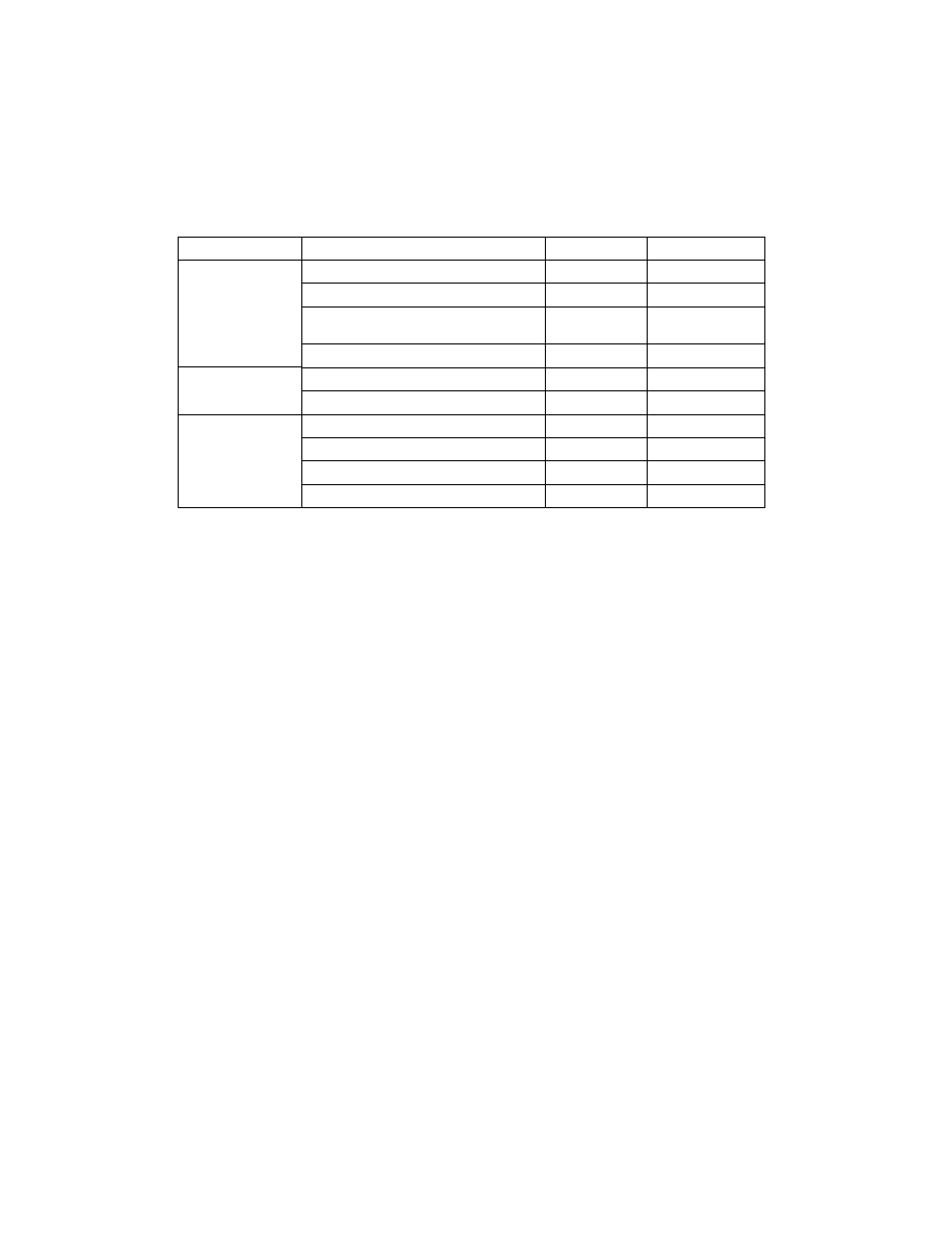

Table 14-8. Encodings of PP, T, and II Sub-Fields

Sub-Field

Transaction

Mnemonic

Binary Encoding

PP (Participation)

Local processor

1

originated request

SRC

00

Local processor

1

responded to request

RES

01

Local processor

1

observed error as third

party

OBS

10

Generic

11

T (Time-out)

Request timed out

TIMEOUT

1

Request did not time out

NOTIMEOUT

0

II (Memory or I/O)

Memory Access

M

00

Reserved

01

I/O

IO

10

Other transaction

11

NOTE:

1. Local processor differentiates the processor reporting the error from other system components (includ-

ing the APIC, other processors, etc.).