H r7). figure 11-2 show, Figure 11-2), st0 po, E b in figure 11-2), st0 poin – Intel IA-32 User Manual

Page 495

Vol. 3A 11-7

INTEL® MMX™ TECHNOLOGY SYSTEM PROGRAMMING

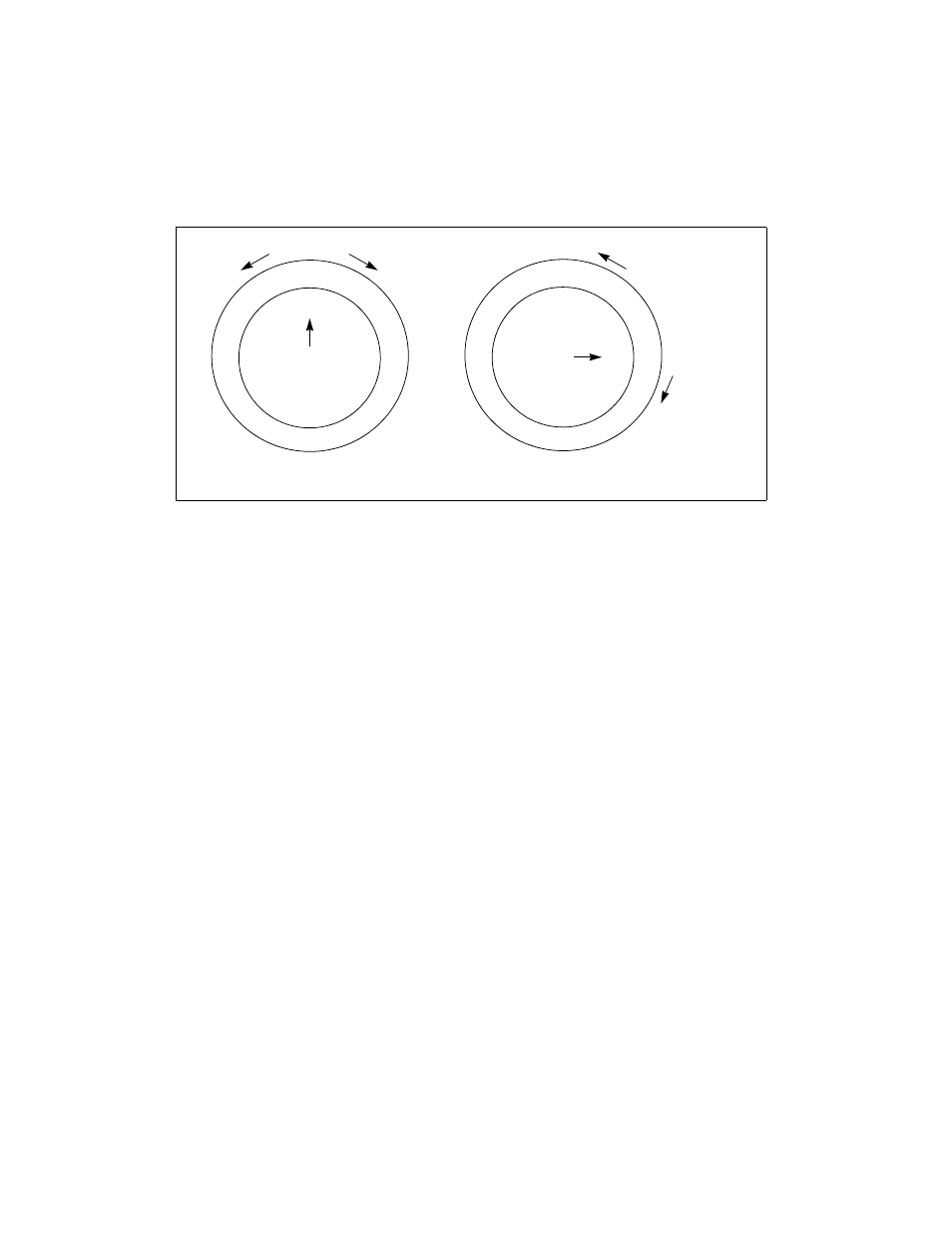

Figure 11-2. Mapping of MMX Registers to x87 FPU Data Register Stack

MM0

MM1

MM2

MM3

MM4

MM5

MM6

MM7

ST1

ST2

ST7

ST0

ST6

ST7

ST1

TOS

TOS

x87 FPU “push”

x87 FPU “pop”

x87 FPU “push”

x87 FPU “pop”

Case A: TOS=0

Case B: TOS=2

MM0

MM1

MM2

MM3

MM4

MM5

MM6

MM7

ST0

Outer circle = x87 FPU data register’s logical location relative to TOS

Inner circle = x87 FPU tags = MMX register’s location = FP registers’s physical location

(R0)

(R2)

(R2)

(R0)

See also other documents in the category Intel Computer Accessories:

- RAID AXXRSBBU6 (14 pages)

- Evaluation Platform Board Manual RN (88 pages)

- ZT8101 (124 pages)

- CELERON 200 (53 pages)

- 210T (24 pages)

- AXXSW1GB (220 pages)

- I/O Controller Hub 6300ESB (14 pages)

- ARCHITECTURE IA-32 (568 pages)

- D15343-003 (166 pages)

- 1520 (176 pages)

- SR1450 (87 pages)

- 410 (60 pages)

- 460T (150 pages)

- SBC-455 (97 pages)

- cPCI-7200 (71 pages)

- 82600 (40 pages)

- 4.0A (10 pages)

- CONTROLLERS 413808 (824 pages)

- IXM5414E (294 pages)

- 520T (31 pages)

- NuPRO-850 (50 pages)

- Ethernet Switch Boards (52 pages)

- Express Hub (4 pages)

- SGI Altix 450 (198 pages)

- OPEN (660) 120/140/150 II (160 pages)

- 130T (18 pages)

- Express 100BASE-T4 (43 pages)

- PCI-7200 (65 pages)

- NetStructure 470 (155 pages)

- EXPRESS 330T (16 pages)

- TOUCH-N-MOW 120000 (12 pages)

- ETX CD (91 pages)

- SRW224P (2 pages)

- 410T (40 pages)