Intel IA-32 User Manual

Page 517

Vol. 3A 13-7

POWER AND THERMAL MANAGEMENT

MSR_THERM2_CTL register is set to 1 (Figure 13-3) and bit 3 of the IA32_MISC_ENABLE

register is set to 1.

Following a power-up or reset, the TM_SELECT flag may be cleared. BIOS is required to

enable either TM1 or TM2. Operating systems and applications must not disable mechanisms

that enable TM1 or TM2. If bit 3 of the IA32_MISC_ENABLE register is set and TM_SELECT

flag of the MSR_THERM2_CTL register is cleared, TM1 is enabled.

On processors introduced after the Pentium 4 processor (this includes most Pentium M proces-

sors), the method used to enable TM2 is different. TM2 is enable by setting bit 13 of

IA32_MISC_ENABLE register to 1.

The target operating frequency and voltage for the TM2 transition after TM2 is triggered is spec-

ified by the value written to MSR_THERM2_CTL, bits 15:0 (Figure 13-4). Following a power-

up or reset, BIOS is required to enable at least one of these two thermal monitoring mechanisms.

If both TM1 and TM2 are supported, BIOS may choose to enable TM2 instead of TM1. Oper-

ating systems and applications must not disable the mechanisms that enable TM1or TM2; and

they must not alter the value in bits 15:0 of the MSR_THERM2_CTL register.

13.4.2.4

Performance State Transitions and Thermal Monitoring

If the thermal control circuitry (TCC) for thermal monitor (TM1/TM2) is active, writes to the

IA32_PERF_CTL will effect a new target operating point as follows:

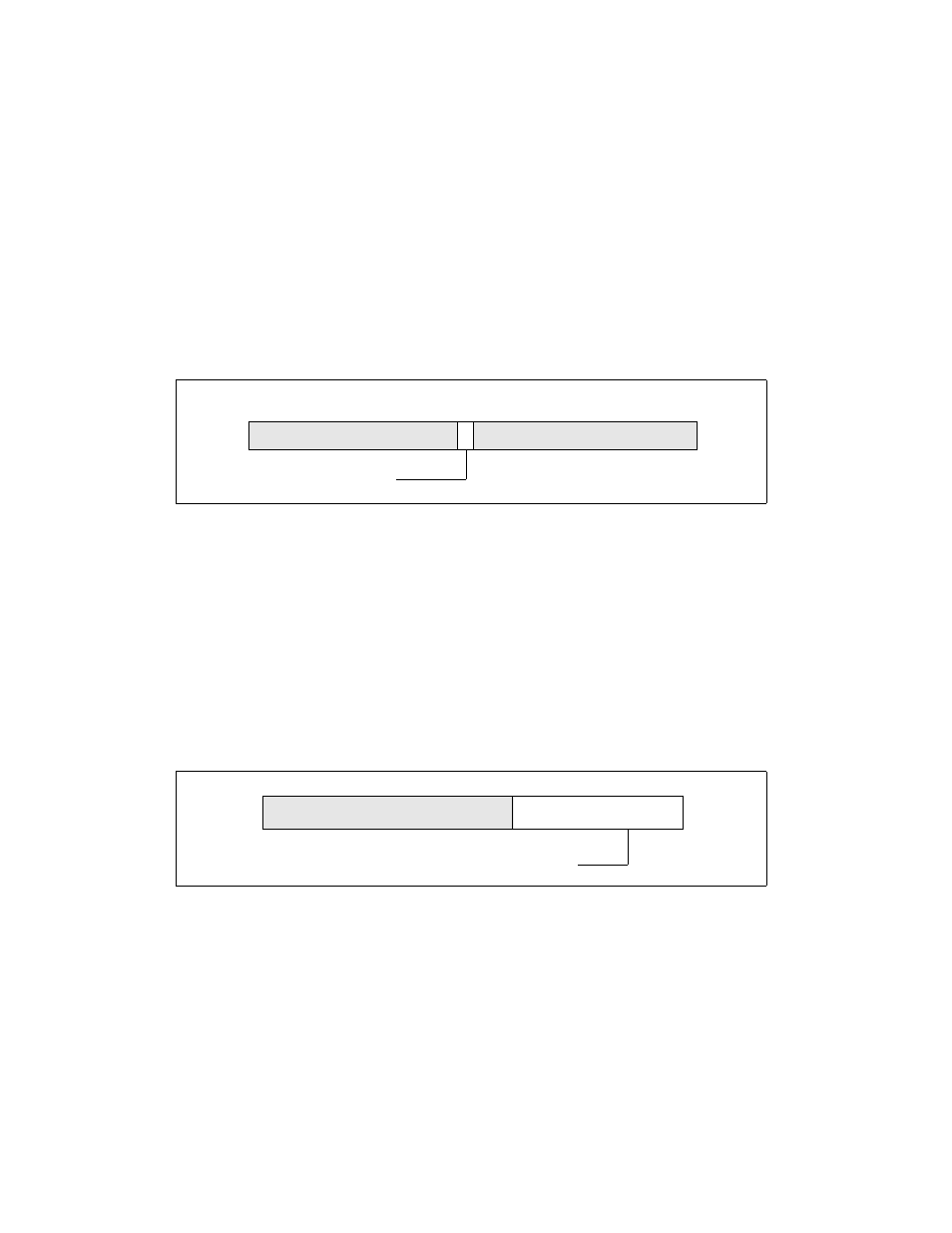

Figure 13-3. MSR_THERM2_CTL Register On Processors with CPUID

Family/Model/Stepping Signature Encoded as 0x69n or 0x6Dn

Figure 13-4. MSR_THERM2_CTL Register for Supporting TM2

TM_SELECT

Reserved

31

0

Reserved

16

63

0

Reserved

15

TM2 Transition Target