8 intel® hyper-threading technology architecture, See section 7.8, “intel, Hyper-threading – Intel IA-32 User Manual

Page 294: Technology architecture”). in, 8 intel, Hyper-threading technology architecture

7-26 Vol. 3A

MULTIPLE-PROCESSOR MANAGEMENT

7.8

INTEL

®

HYPER-THREADING TECHNOLOGY

ARCHITECTURE

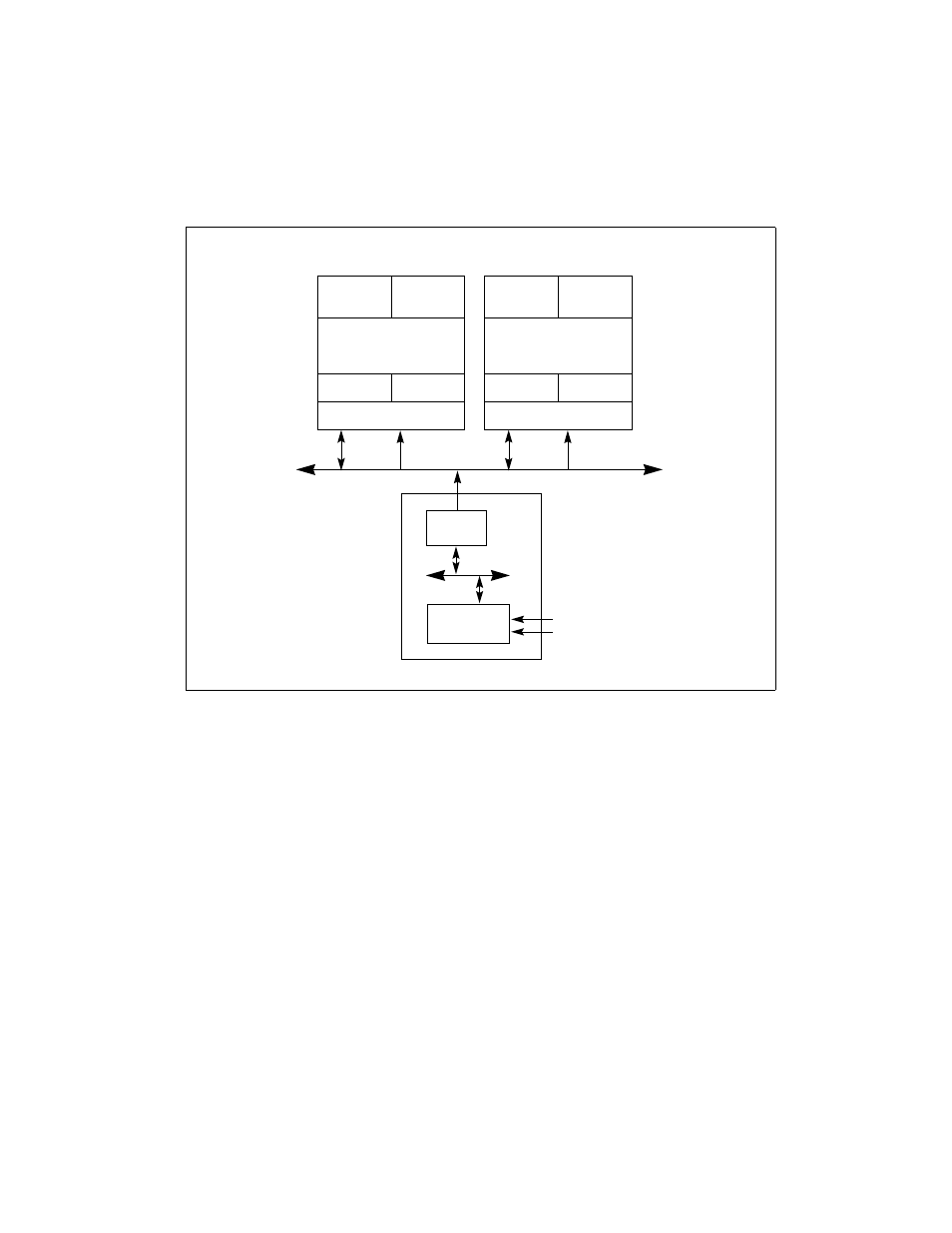

Figure 7-4 shows a generalized view of an IA-32 processor supporting Hyper-Threading Tech-

nology, using the Intel Xeon processor MP as an example. This implementation of the Hyper-

Threading Technology consists of two logical processors (each represented by a separate IA-32

architectural state) which share the processor’s execution engine and the bus interface. Each

logical processor also has its own advanced programmable interrupt controller (APIC).

Figure 7-3. Local APICs and I/O APIC in MP System Supporting HT Technology

I/O APIC

External

Interrupts

System Chip Set

Bridge

PCI

Interrupt Messages

Local APIC

Logical

Processor 0

Local APIC

Logical

Processor 1

Hyper-Threading Technology

IA-32 Processor with

Bus Interface

Processor Core

IPIs

Interrupt

Messages

Local APIC

Logical

Processor 0

Local APIC

Logical

Processor 1

Hyper-Threading Technology

IA-32 Processor with

Bus Interface

Processor Core

IPIs

Interrupt

Messages