Figure 9-3 sh, Table 9-4 – Intel IA-32 User Manual

Page 395

Vol. 3A 9-21

PROCESSOR MANAGEMENT AND INITIALIZATION

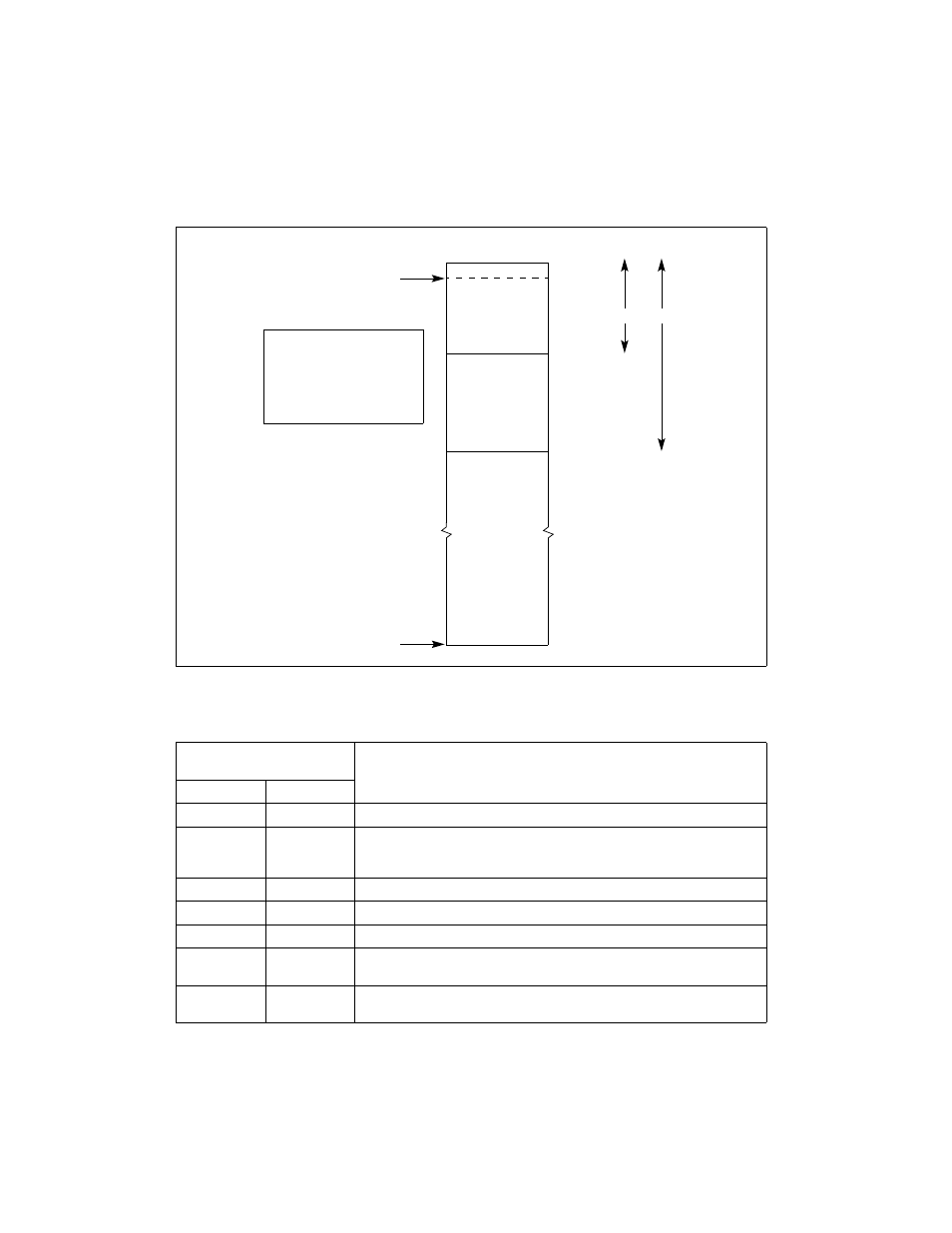

Figure 9-3. Processor State After Reset

Table 9-4. Main Initialization Steps in STARTUP.ASM Source Listing

STARTUP.ASM Line

Numbers

Description

From

To

157

157

Jump (short) to the entry code in the EPROM

162

169

Construct a temporary GDT in RAM with one entry:

0 - null

1 - R/W data segment, base = 0, limit = 4 GBytes

171

172

Load the GDTR to point to the temporary GDT

174

177

Load CR0 with PE flag set to switch to protected mode

179

181

Jump near to clear real mode instruction queue

184

186

Load DS, ES registers with GDT[1] descriptor, so both point to the entire

physical memory space

188

195

Perform specific board initialization that is imposed by the new protected

mode

0

FFFF FFFFH

After Reset

[CS.BASE+EIP]

FFFF FFF0H

EIP = 0000 FFF0H

[SP, DS, SS, ES]

FFFF 0000H

64K EPROM

CS.BASE = FFFF 0000H

DS.BASE = 0H

ES.BASE = 0H

SS.BASE = 0H

ESP = 0H