Table 10-8 s – Intel IA-32 User Manual

Page 465

Vol. 3A 10-25

MEMORY CACHE CONTROL

ization software should then set the MTRRs to a specific, system-defined memory map. Typi-

cally, the BIOS (basic input/output system) software configures the MTRRs. The operating

system or executive is then free to modify the memory map using the normal page-level cache-

ability attributes.

In a multiprocessor system, different Pentium 4, Intel Xeon, or P6 family processors MUST use

the identical MTRR memory map so that software has a consistent view of memory, indepen-

dent of the processor executing a program.

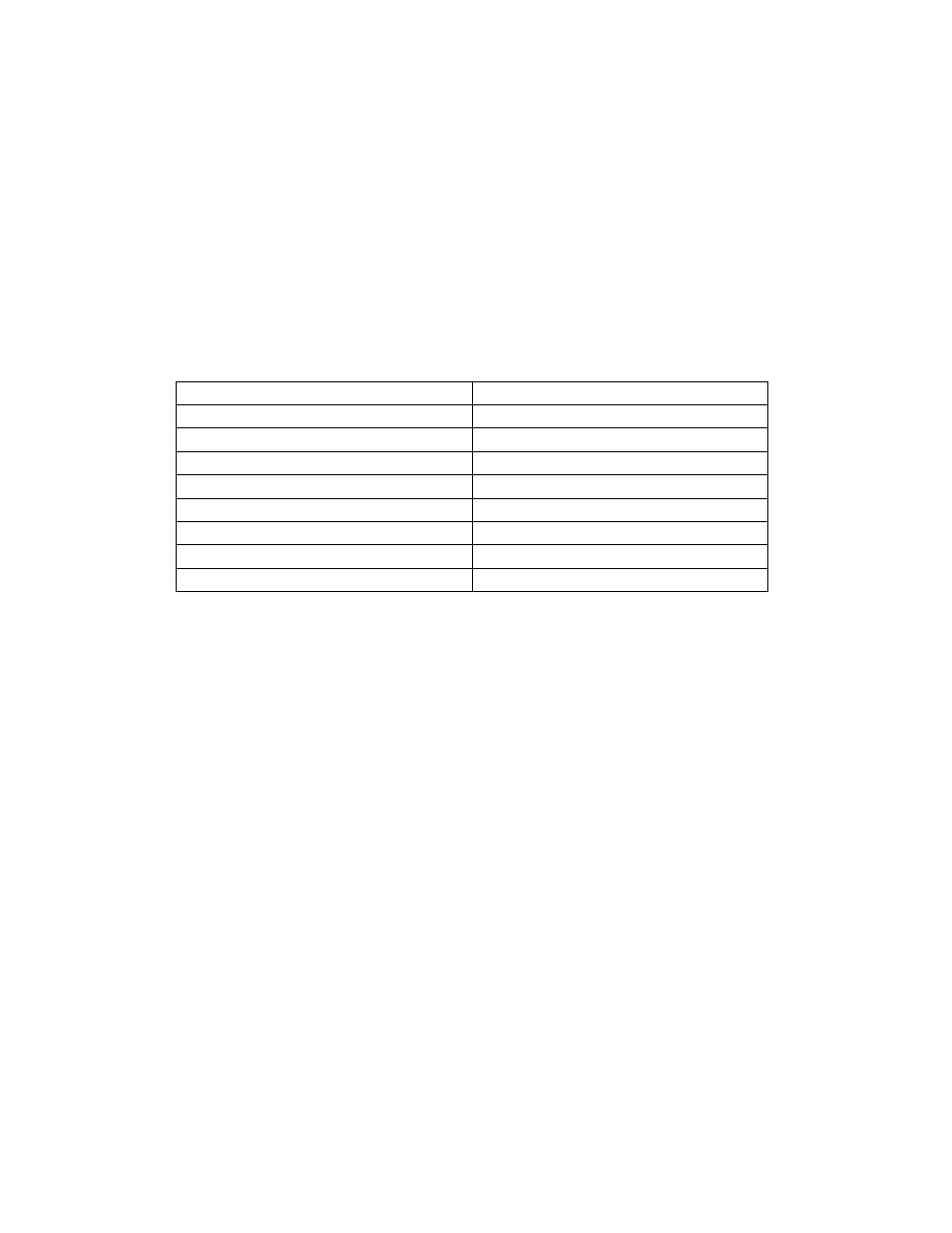

Table 10-8. Memory Types That Can Be Encoded in MTRRs

Memory Type and Mnemonic

Encoding in MTRR

Uncacheable (UC)

00H

Write Combining (WC)

01H

Reserved*

02H

Reserved*

03H

Write-through (WT)

04H

Write-protected (WP)

05H

Writeback (WB)

06H

Reserved*

7H through FFH

NOTE:

* Use of these encodings results in a general-protection exception (#GP).