12 translation lookaside buffers (tlbs) – Intel IA-32 User Manual

Page 126

3-46 Vol. 3A

PROTECTED-MODE MEMORY MANAGEMENT

3.12

TRANSLATION LOOKASIDE BUFFERS (TLBS)

The processor stores the most recently used page-directory and page-table entries in on-chip

caches called translation lookaside buffers or TLBs. The P6 family and Pentium processors have

separate TLBs for the data and instruction caches. Also, the P6 family processors maintain sepa-

rate TLBs for 4-KByte and 4-MByte page sizes. The CPUID instruction can be used to deter-

mine the sizes of the TLBs provided in the P6 family and Pentium processors.

Most paging is performed using the contents of the TLBs. Bus cycles to the page directory and

page tables in memory are performed only when the TLBs do not contain the translation infor-

mation for a requested page.

The TLBs are inaccessible to application programs and tasks (privilege level greater than 0); that

is, they cannot invalidate TLBs. Only, operating system or executive procedures running at priv-

ilege level of 0 can invalidate TLBs or selected TLB entries. Whenever a page-directory or

page-table entry is changed (including when the present flag is set to zero), the operating-system

must immediately invalidate the corresponding entry in the TLB so that it can be updated the

next time the entry is referenced.

All of the (non-global) TLBs are automatically invalidated any time the CR3 register is loaded

(unless the G flag for a page or page-table entry is set, as describe later in this section). The CR3

register can be loaded in either of two ways:

•

Explicitly, using the MOV instruction, for example:

MOV CR3, EAX

where the EAX register contains an appropriate page-directory base address.

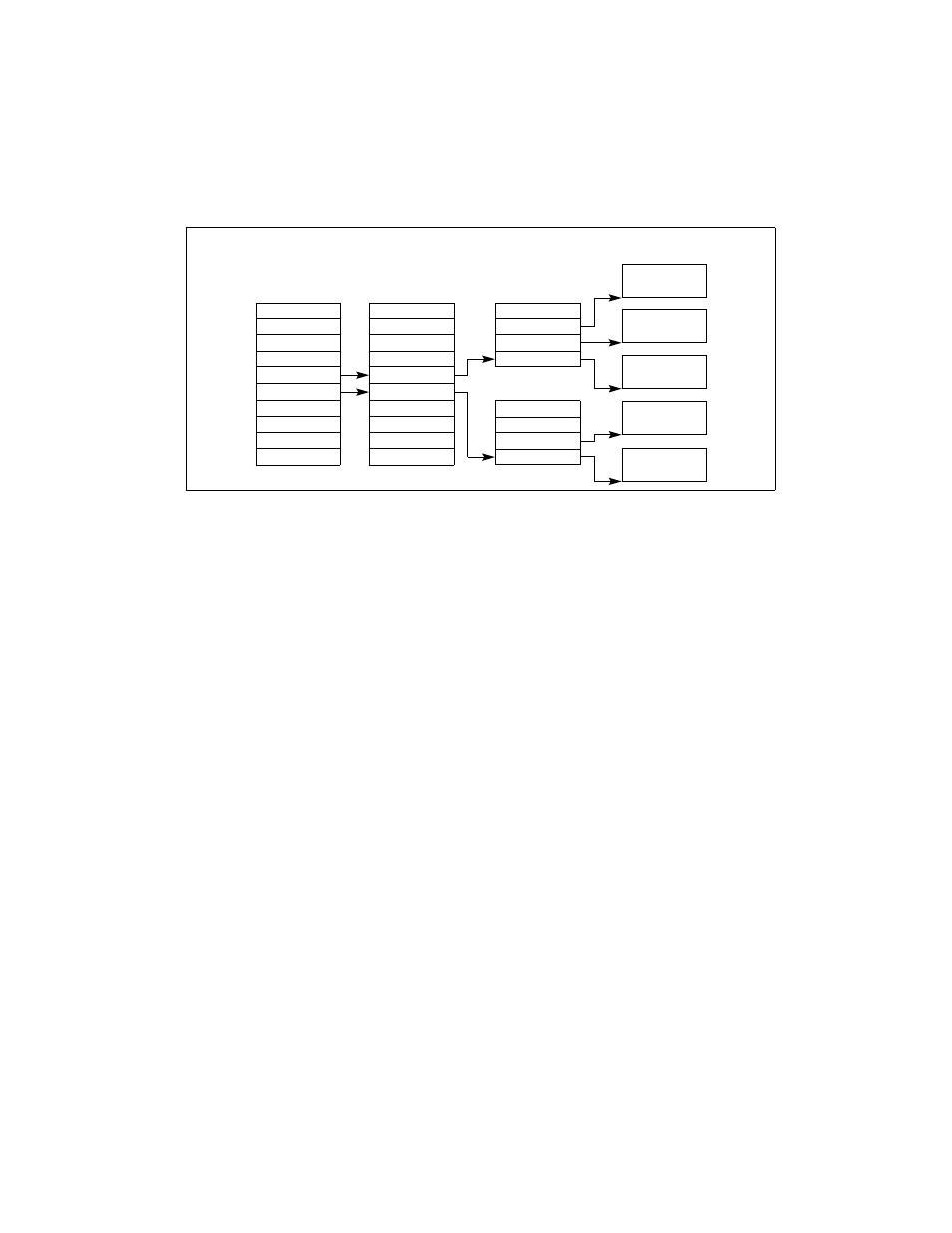

Figure 3-28. Memory Management Convention That Assigns a Page Table

to Each Segment

Seg. Descript.

LDT

Seg. Descript.

PDE

Page Directory

PDE

PTE

PTE

PTE

PTE

PTE

Page s

Page Frames