3 enhanced paging data structures – Intel IA-32 User Manual

Page 121

Vol. 3A 3-41

PROTECTED-MODE MEMORY MANAGEMENT

•

Page-directory entry — Bits 29:21 provide an offset to an entry in the page directory. The

selected entry provides the base physical address of a 2-MByte page.

•

Page offset — Bits 20:0 provides an offset to a physical address in the page.

3.10.3

Enhanced Paging Data Structures

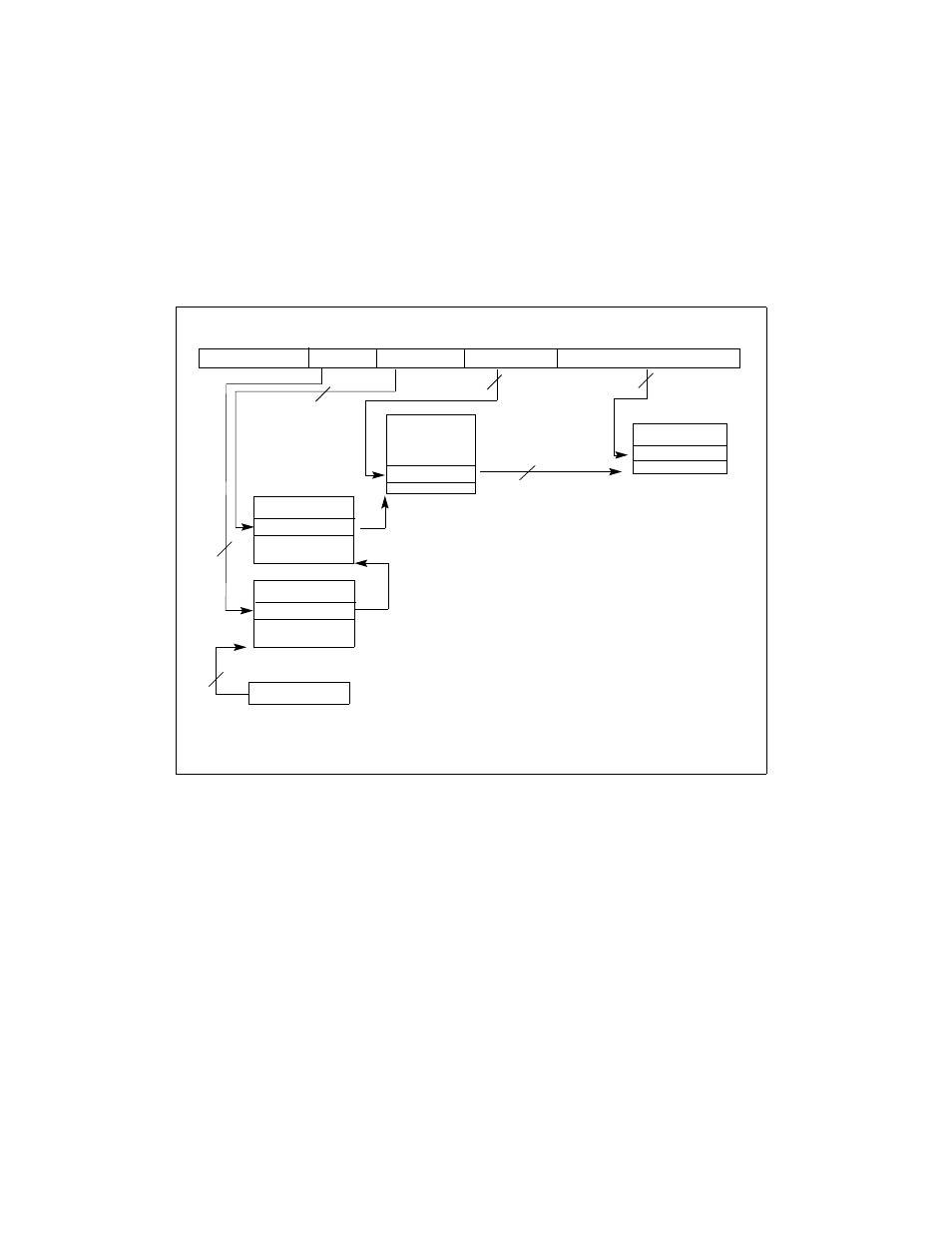

Figure 3-26 shows the format for the PML4 table, page-directory-pointer table, page-direc-

tory and page-table entries when 4-KByte pages are used in IA-32e mode. Figure 3-27

shows the format for the PML4 table, the page-directory-pointer table and page-directory

entries when 2-MByte pages are used in IA-32e mode.

Except for the PML4 table, these enhanced formats of page-directory-pointer table, page-

directory, and page-table entries are also used in enhanced legacy PAE-enabled paging on

processors that supports Intel EM64T (see Section 3.8.1, “Enhanced Legacy PAE Paging”).

Figure 3-25. IA-32e Mode Paging Structures (2-MByte pages)

Directory Ptr

Linear Address

Dir. Pointer Entry

CR3 (PML4)

39 38

Pointer Table

512 PML4 *512 PDPTE

∗ 512 PDE = 2

27

Pages

9

9

40

1

21

1. 40 bits aligned onto a 4-KByte boundary

19

2-MByte Page

Offset

Physical Addr

Directory Entry

0

20

21

Directory

30 29

Page-Directory-

Page-Directory

PML4

47

48

63

Sign Extended

9

PML4 Entry

NOTE: