2 logical destination mode – Intel IA-32 User Manual

Page 353

Vol. 3A 8-29

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

NOTE

The number of local APICs that can be addressed on the system bus may be

restricted by hardware.

8.6.2.2

Logical Destination Mode

In logical destination mode, IPI destination is specified using an 8-bit message destination

address (MDA), which is entered in the destination field of the ICR. Upon receiving an IPI

message that was sent using logical destination mode, a local APIC compares the MDA in the

message with the values in its LDR and DFR to determine if it should accept and handle the IPI.

For both configurations of logical destination mode, when combined with lowest priority

delivery mode, software is responsible for ensuring that all of the local APICs included in or

addressed by the IPI or I/O subsystem interrupt are present and enabled to receive the interrupt.

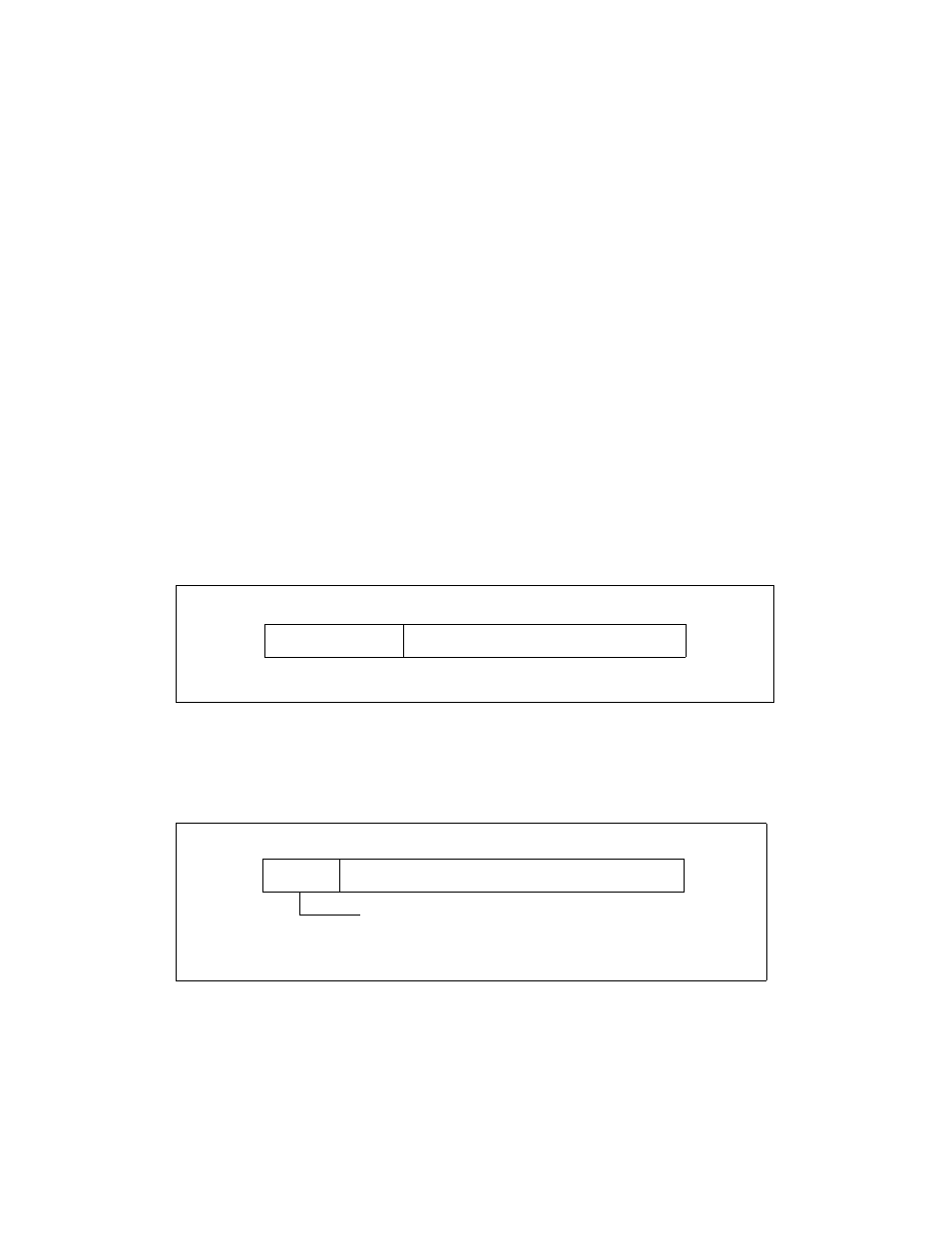

Figure 8-13 shows the layout of the logical destination register (LDR). The 8-bit logical APIC

ID field in this register is used to create an identifier that can be compared with the MDA.

NOTE

The logical APIC ID should not be confused with the local APIC ID that is

contained in the local APIC ID register.

Figure 8-14 shows the layout of the destination format register (DFR). The 4-bit model field in

this register selects one of two models (flat or cluster) that can be used to interpret the MDA

when using logical destination mode.

Figure 8-13. Logical Destination Register (LDR)

Figure 8-14. Destination Format Register (DFR)

31

0

23

24

Reserved

Logical APIC ID

Address: 0FEE0 00D0H

Value after reset: 0000 0000H

31

0

Model

28

Reserved (All 1s)

Address: 0FEE0 00E0H

Value after reset: FFFF FFFFH

Flat model: 1111B

Cluster model: 0000B