Advanced programmable interrupt controller (apic) – Intel IA-32 User Manual

Page 359

Vol. 3A 8-35

ADVANCED PROGRAMMABLE INTERRUPT CONTROLLER (APIC)

1.

(IPIs only) It examines the IPI message to determines if it is the specified destination for

the IPI as described in Section 8.6.2, “Determining IPI Destination.” If it is the specified

destination, it continues its acceptance procedure; if it is not the destination, it discards the

IPI message. When the message specifies lowest-priority delivery mode, the local APIC

will arbitrate with the other processors that were designated on recipients of the IPI

message (see Section 8.6.2.4, “Lowest Priority Delivery Mode”).

2.

If the local APIC determines that it is the designated destination for the interrupt and if the

interrupt request is an NMI, SMI, INIT, ExtINT, or INIT-deassert interrupt, or one of the

MP protocol IPI messages (BIPI, FIPI, and SIPI), the interrupt is sent directly to the

processor core for handling.

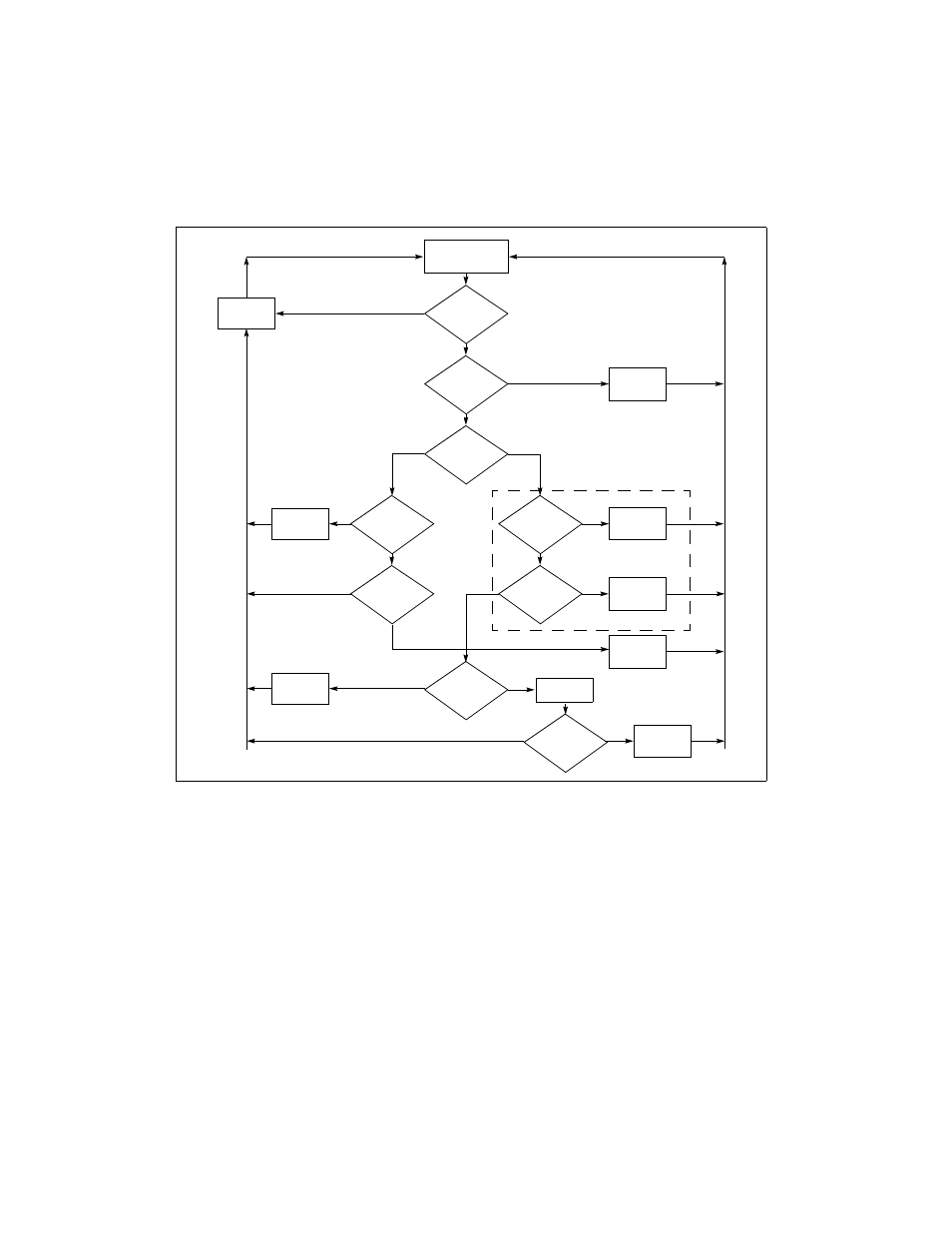

Figure 8-17. Interrupt Acceptance Flow Chart for the Local APIC (P6 Family and

Pentium Processors)

Wait to Receive

Bus Message

Belong

to

Destination?

Is it

NMI/SMI/INIT

/

ExtINT?

Delivery

Mode?

Am

I

Focus?

Other

Focus?

Is Interrupt

Slot Available?

Is Status

a Retry?

Discard

Message

Accept

Message

Yes

Yes

Accept

Message

Is

Interrupt Slot

Available?

Arbitrate

Yes

Am I

Winner?

Accept

Message

Yes

No

Set Status

to Retry

No

No

Yes

Set Status

to Retry

No

Discard

Message

No

Accept

Message

Yes

Lowest

Priority

Fixed

Yes

No

No

Yes

No

P6 Family

Processor Specific