1 enhanced legacy pae paging – Intel IA-32 User Manual

Page 111

Vol. 3A 3-31

PROTECTED-MODE MEMORY MANAGEMENT

When the PAE paging mechanism is enabled, the processor supports two sizes of pages:

4-KByte and 2-MByte. As with 32-bit addressing, both page sizes can be addressed within the

same set of paging tables (that is, a page-directory entry can point to either a 2-MByte page or

a page table that in turn points to 4-KByte pages). To support the 36-bit physical addresses, the

following changes are made to the paging data structures:

•

The paging table entries are increased to 64 bits to accommodate 36-bit base physical

addresses. Each 4-KByte page directory and page table can thus have up to 512 entries.

•

A new table, called the page-directory-pointer table, is added to the linear-address

translation hierarchy. This table has 4 entries of 64-bits each, and it lies above the page

directory in the hierarchy. With the physical address extension mechanism enabled, the

processor supports up to 4 page directories.

•

The 20-bit page-directory base address field in register CR3 (PDBR) is replaced with a

27-bit page-directory-pointer-table base address field. The updated field provides the 27

most-significant bits of the physical address of the first byte of the page-directory pointer

table (forcing the table to be located on a 32-byte boundary).

Since CR3 now contains the page-directory-pointer-table base address, it can be referred to

as the page-directory-pointer-table register (PDPTR). See Figure 3-17.

•

Linear address translation is changed to allow mapping 32-bit linear addresses into the

larger physical address space.

3.8.1

Enhanced Legacy PAE Paging

On processors that support Intel EM64T, the page directory pointer entry supports physical

address size of the underlying implementation (reported by CPUID.80000008H). Legacy PAE

enabled paging (see Section 3.8.2, “Linear Address Translation With PAE Enabled (4-KByte

Pages)” and Section 3.8.3, “Linear Address Translation With PAE Enabled (2-MByte Pages)”

can address physical memory greater than 64-GByte if the implementation’s physical address

size is greater than 36 bits and if the processor supports Intel EM64T.

3.8.2

Linear Address Translation With PAE Enabled (4-KByte

Pages)

Figure 3-18 shows the page-directory-pointer, page-directory, and page-table hierarchy when

mapping linear addresses to 4-KByte pages when the PAE paging mechanism enabled. This

paging method can be used to address up to 2

20

pages, which spans a linear address space of 2

32

bytes (4 GBytes).

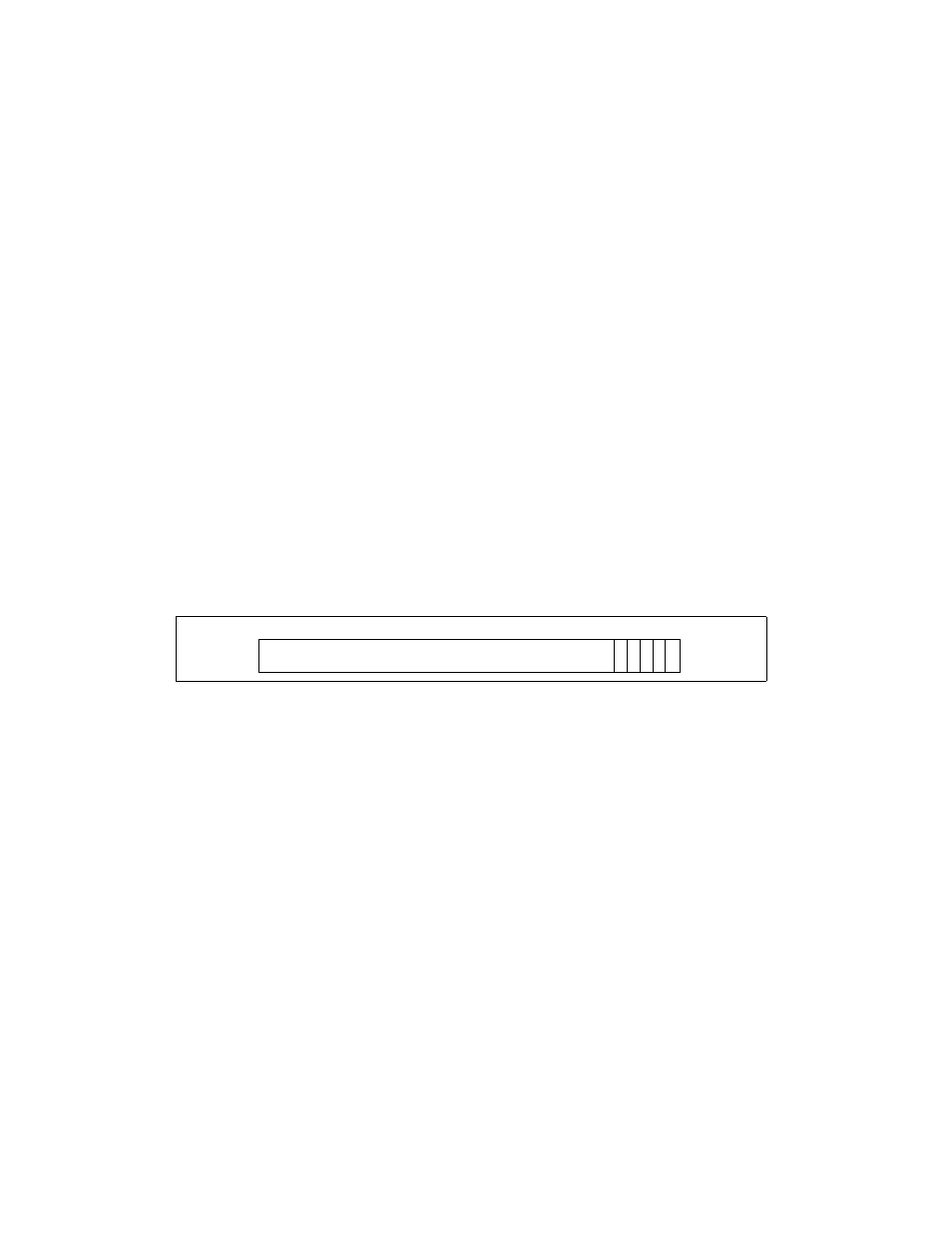

Figure 3-17. Register CR3 Format When the Physical Address Extension is Enabled

31

0

0

Page-Directory-Pointer-Table Base Address

P

C

D

P

W

T

0

0