Intel IA-32 User Manual

Page 51

Vol. 3A 2-3

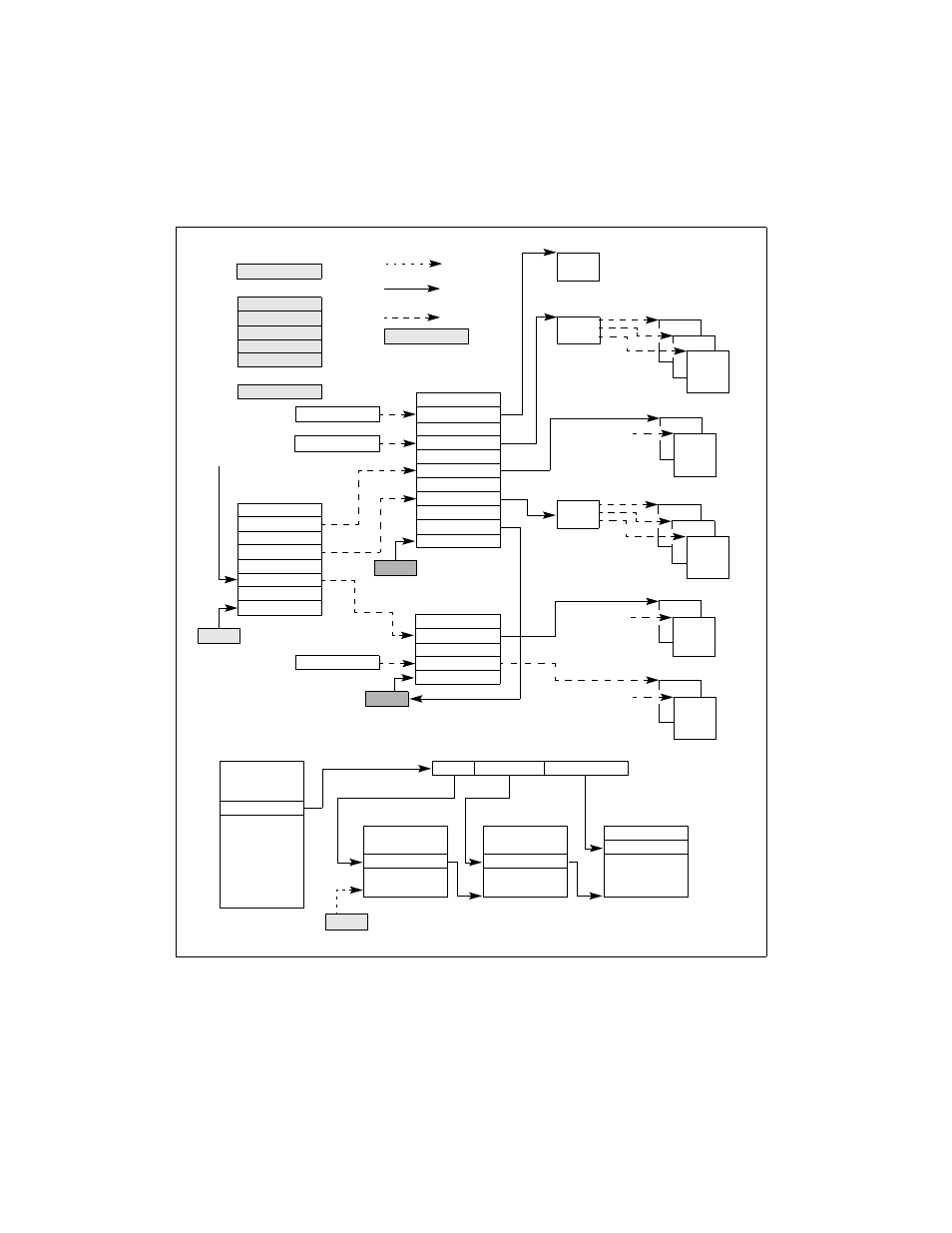

SYSTEM ARCHITECTURE OVERVIEW

Figure 2-1. IA-32 System-Level Registers and Data Structures

Local Descriptor

Table (LDT)

EFLAGS Register

Control Registers

CR1

CR2

CR3

CR4

CR0

Global Descriptor

Table (GDT)

Interrupt Descriptor

Table (IDT)

IDTR

GDTR

Interrupt Gate

Trap Gate

LDT Desc.

TSS Desc.

Code

Stack

Code

Stack

Code

Stack

Task-State

Segment (TSS)

Code

Data

Stack

Task

Interrupt Handler

Exception Handler

Protected Procedure

TSS Seg. Sel.

Call-Gate

Segment Selector

Dir

Table

Offset

Linear Address

Page Directory

Pg. Dir. Entry

Linear Address Space

Linear Addr.

0

Seg. Desc.

Segment Sel.

Code, Data or

Stack Segment

Interrupt

Vector

TSS Desc.

Seg. Desc.

Task Gate

Current

TSS

Call Gate

Task-State

Segment (TSS)

Code

Data

Stack

Task

Seg. Desc.

Current

TSS

Current

TSS

Segment Selector

Linear Address

Task Register

CR3*

Page Table

Pg. Tbl. Entry

Page

Physical Addr.

LDTR

This page mapping example is for 4-KByte pages

and the normal 32-bit physical address size.

Register

*Physical Address

Physical Address