1 state of the logical processors – Intel IA-32 User Manual

Page 295

Vol. 3A 7-27

MULTIPLE-PROCESSOR MANAGEMENT

7.8.1

State of the Logical Processors

The following features are part of the architectural state of logical processors within IA-32

processors supporting Hyper-Threading Technology. The features can be subdivided into three

groups:

•

Duplicated for each logical processor

•

Shared by logical processors in a physical processor

•

Shared or duplicated, depending on the implementation

The following features are duplicated for each logical processor:

•

General purpose registers (EAX, EBX, ECX, EDX, ESI, EDI, ESP, and EBP)

•

Segment registers (CS, DS, SS, ES, FS, and GS)

•

EFLAGS and EIP registers. Note that the CS and EIP registers for each logical processor

point to the instruction stream for the thread being executed by the logical processor.

•

x87 FPU registers (ST0 through ST7, status word, control word, tag word, data operand

pointer, and instruction pointer)

•

MMX registers (MM0 through MM7)

•

XMM registers (XMM0 through XMM7) and the MXCSR register

•

Control registers (CR0, CR2, CR3, CR4) and system table pointer registers (GDTR,

LDTR, IDTR, task register)

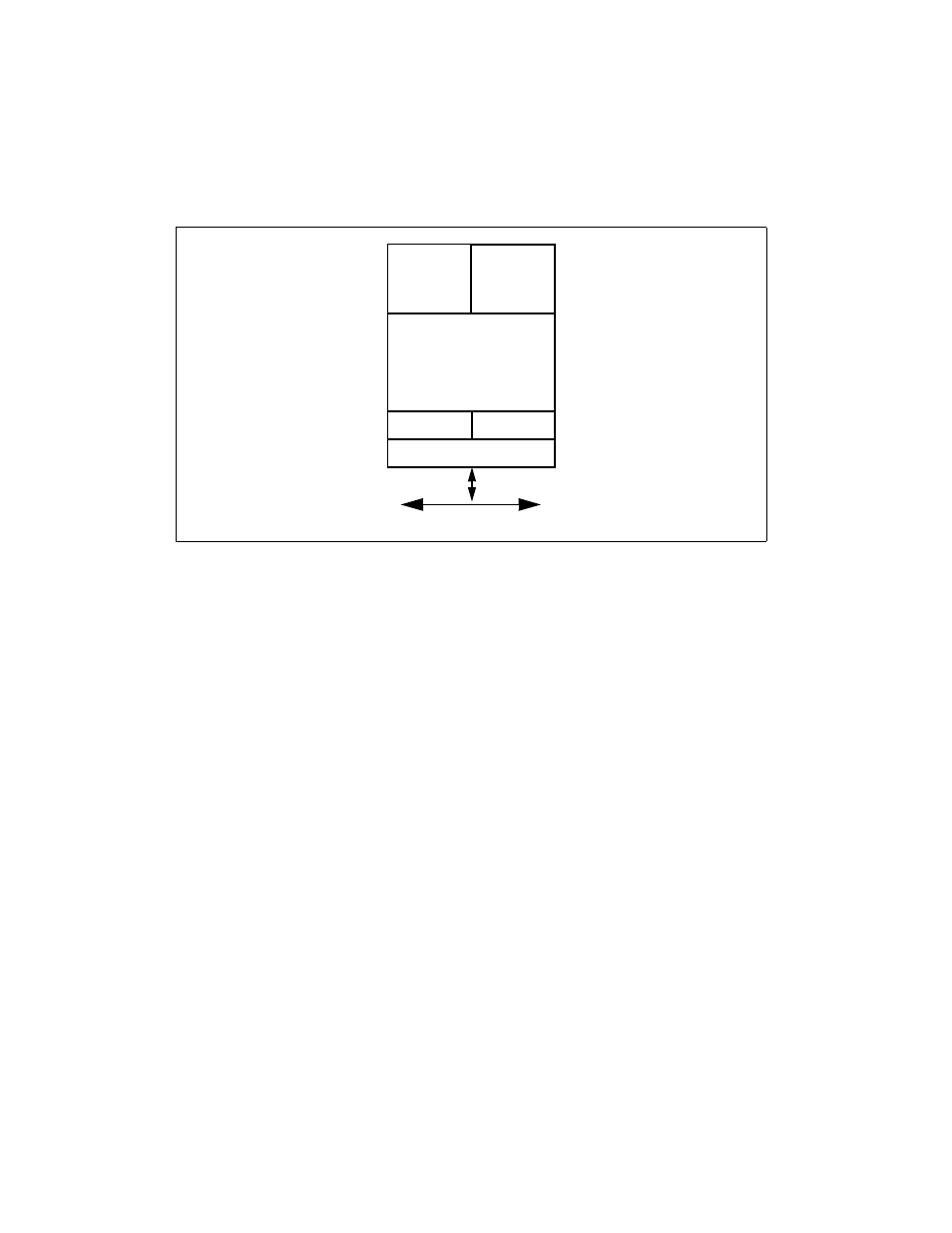

Figure 7-4. IA-32 Processor with Two Logical Processors Supporting HT Technology

Logical

Processor 0

Architectural

State

Bus Interface

Local APIC

Local APIC

Logical

Processor 1

Architectural

State

Execution Engine

System Bus