Intel IA-32 User Manual

Page 542

14-16 Vol. 3A

MACHINE-CHECK ARCHITECTURE

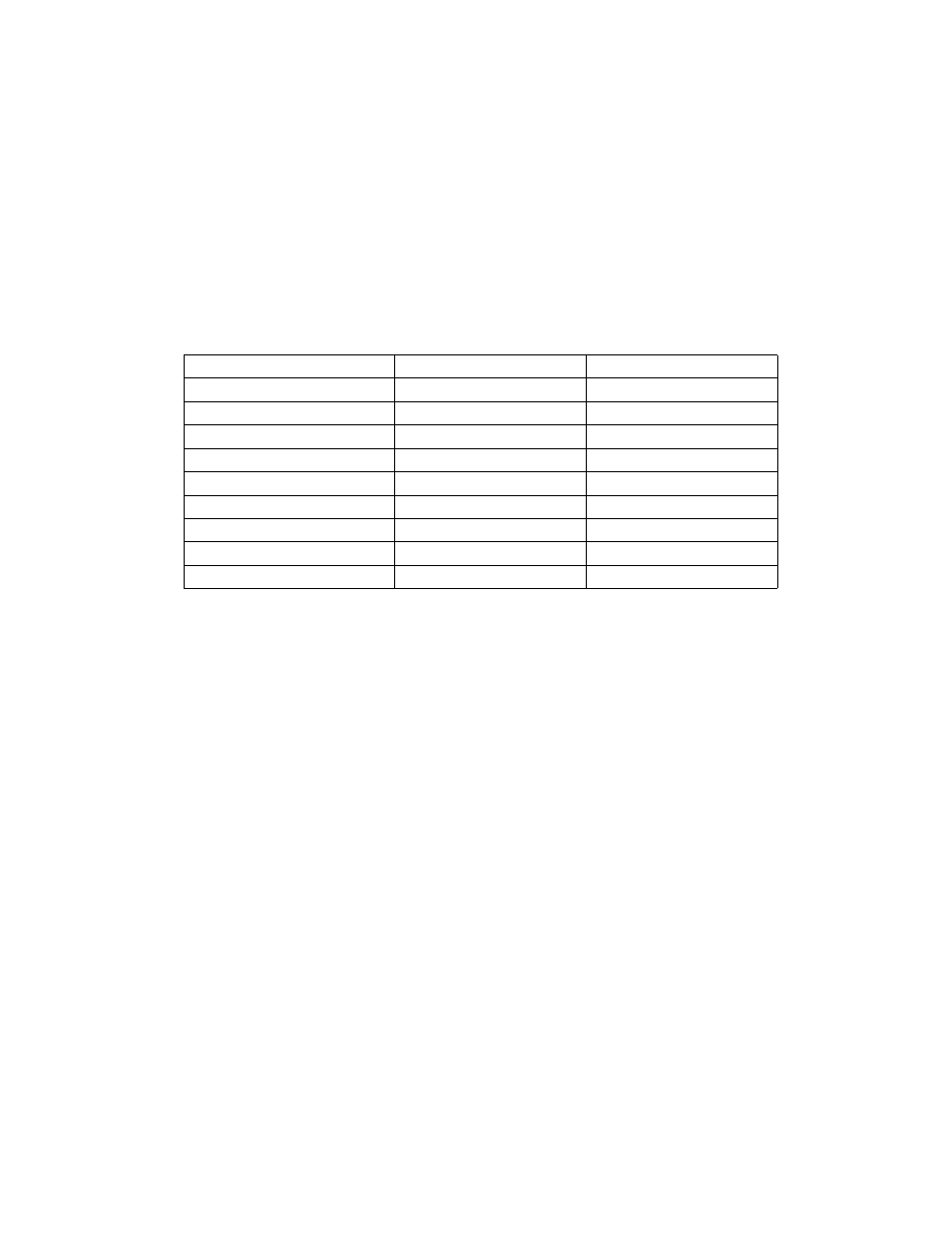

The 4-bit RRRR sub-field (see Table 14-7) indicates the type of action associated with the error.

Actions include read and write operations, prefetches, cache evictions, and snoops. Generic

error is returned when the type of error cannot be determined. Generic read and generic write

are returned when the processor cannot determine the type of instruction or data request that

caused the error. Eviction and snoop requests apply only to the caches. All of the other requests

apply to TLBs, caches and interconnects.

The bus and interconnect errors are defined with the 2-bit PP (participation), 1-bit T (time-

out), and 2-bit II (memory or I/O) sub-fields, in addition to the LL and RRRR sub-fields (see

Table 14-8). The bus error conditions are implementation dependent and related to the type of

bus implemented by the processor. Likewise, the interconnect error conditions are predicated

on a specific implementation-dependent interconnect model that describes the connections

between the different levels of the storage hierarchy. The type of bus is implementation depen-

dent, and as such is not specified in this document. A bus or interconnect transaction consists

of a request involving an address and a response.

Table 14-7. Encoding of Request (RRRR) Sub-Field

Request Type

Mnemonic

Binary Encoding

Generic Error

ERR

0000

Generic Read

RD

0001

Generic Write

WR

0010

Data Read

DRD

0011

Data Write

DWR

0100

Instruction Fetch

IRD

0101

Prefetch

PREFETCH

0110

Eviction

EVICT

0111

Snoop

SNOOP

1000