3 multiple interrupts, Multiple interrupts – FUJITSU F2MC-8L F202RA User Manual

Page 55

39

CHAPTER 3 CPU

3.4.3

Multiple Interrupts

Multiple interrupts are allowed by setting different levels into the interrupt level setting

registers (ILR1 to ILR4) for multiple interrupt requests from peripheral functions.

■

Multiple Interrupts

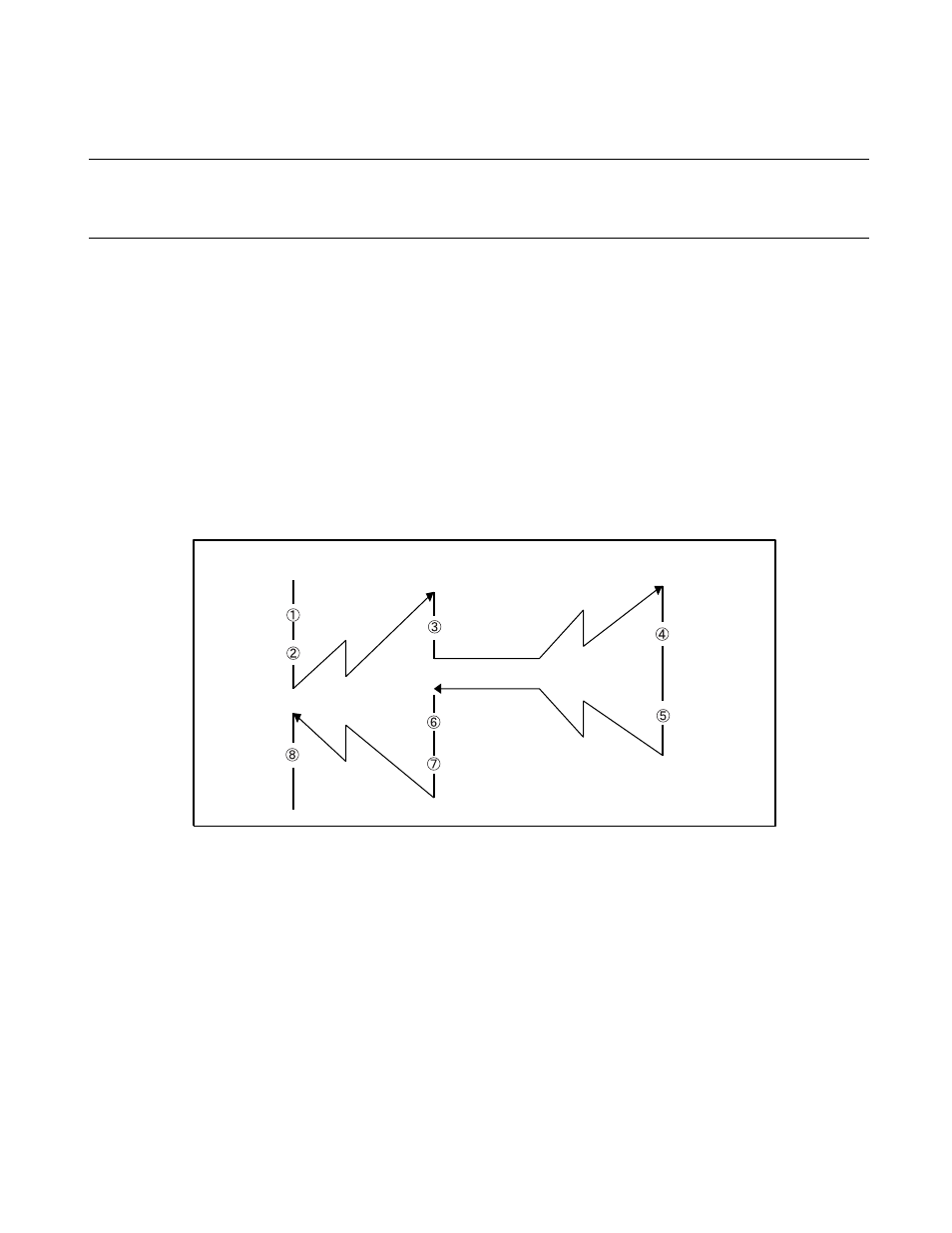

When an interrupt request with a higher interrupt level is generated while the interrupt processing routine is

operating, the current interrupt processing cycle is stopped to accept the higher-level interrupt request.

Interrupt levels 1, 2, and 3 can be specified. Level 3 prohibits the CPU from accepting interrupts.

●

Example of multiple interrupts

As an example of multiple-interrupt processing, suppose a case in which a timer interrupt has precedence

using the A/D interrupt, and the A/D interrupt level is set to level 2 and the timer interrupt level is set to

level 1. Figure 3.4-3 shows the sequence performed when an external interrupt is generated while an A/D

interrupt is being processed.

Figure 3.4-3 Example of Multiple Interrupts

•

In the A/D interrupt processing, the interrupt level bits in the condition code register (CCR: IL1 and

IL0) are set to the same value as the value in the interrupt level setting register corresponding to the A/

D interrupt (ILR1, 2, 3, or 4) (i.e., 2 in this example). If an interrupt request with a higher interrupt level

specified is generated (1 in this example), processing for the higher interrupt level is effected first.

•

To temporarily prohibit multiple interrupts in the A/D interrupt processing, turn off the interrupt enable

flag (CCR: I = 0) in the condition code register, or set 00

B

to the interrupt level bits (IL1 and IL0).

•

Executing the return instruction (RETI) after interrupt processing restores the values of the program

counter (PC) and program status (PS) and ensures resumption of the interrupted program.

•

The value in the condition code register (CCR) is returned to the value used before interruption when

the program status (PS) value is restored.

Main program

Initializes

peripherals

A/D interrupt

generated

Main

program

restarts

Interrupt

level 2

A/D interrupt

processing

Timer interrupt

generated

Stop

process-

ing

Resumes

processing

A/D interrupt

processed

Return from A/D

interrupt processing

Interrupt

level 1

Timer interrupt

processing

Timer interrupt

processed

Return from

timer interrupt

processing