Block diagram of port 0, Registers pdr0, ddr0, and pul0 of port 0 – FUJITSU F2MC-8L F202RA User Manual

Page 95

79

CHAPTER 4 I/O PORTS

■

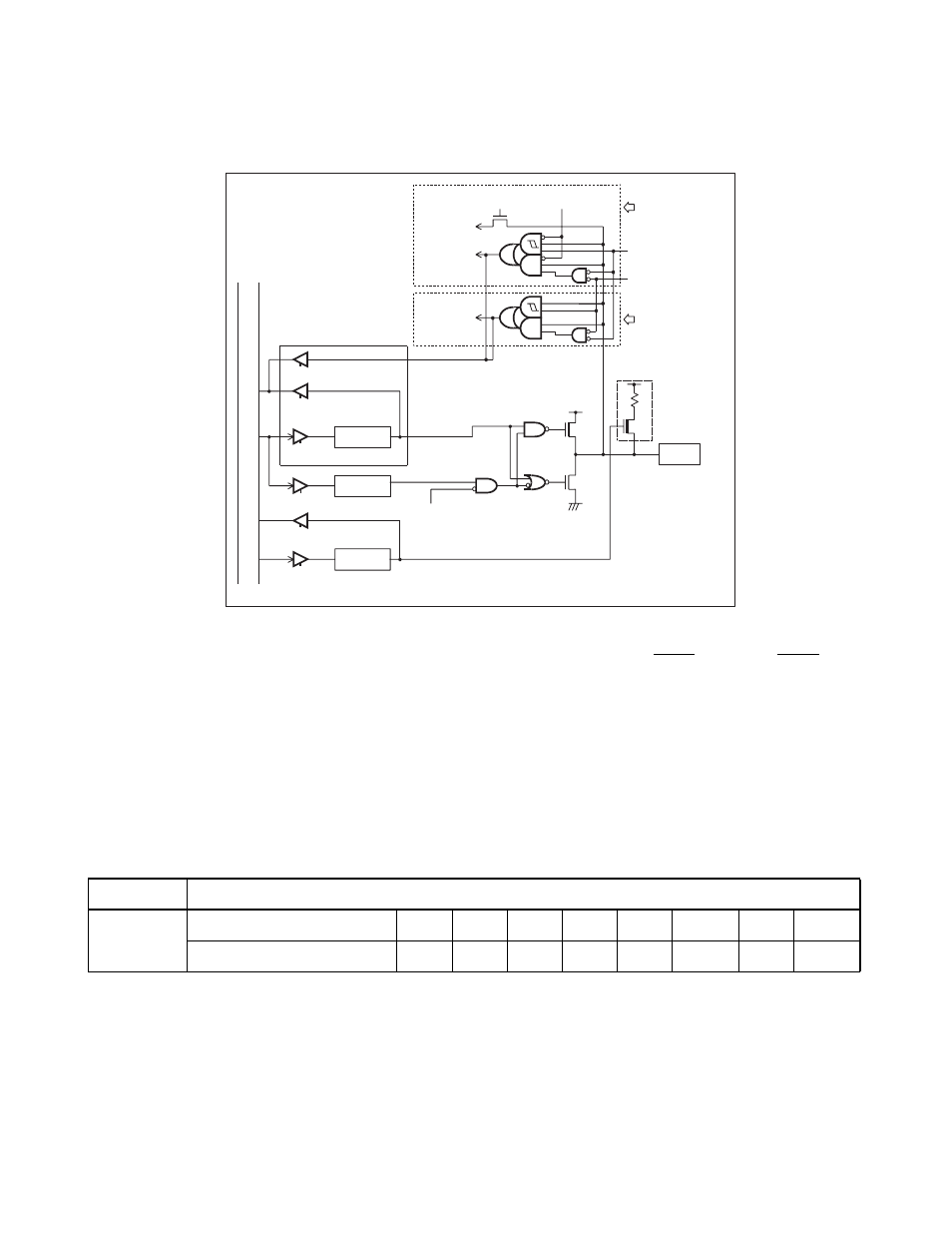

Block Diagram of Port 0

Figure 4.2-1 Block Diagram of Port 0

Note:

When the A/D converter is used, deselect pull-up action for pins P03/INT23/AN7 to P00/INT20/AN4.

Pins set to be used as analog input pins must not be used as an output port.

■

Registers PDR0, DDR0, and PUL0 of Port 0

Registers PDR0, DDR0, and PUL0 are associated with port 0.

The bits of these registers correspond to the pins of port 0 in one-to-one correspondence.

Table 4.2-2 tabulates the correspondence between the pins and the bits of the port 0 registers.

DDR

Pch

Nch

PDR

PUL

SPL: Pin status setting bit of standby control register (STBC)

(SPL=1)

A/D converter

channel select

A/D converter

enable bit

A/D input occurring

To A/D

converter's

analog input

External

interrupt

From external

interrupt enable

Stop mode

No A/D input

Pull-up

resistor

External

interrupt

Pins

Inter

nal data b

u

s

PDR read

PDR read

(when read-modify-write is

performed)

PDR write

Output latch

DDR write

PUL read

PUL write

(SPL=1)

Stop mode

Table 4.2-2 Correspondence between the Pins and the Bits of the Port 0 Registers

Port name

Bits of associated registers and corresponding pins

Port 0

PDR0, DDR0, PUL0

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Pin corresponding to bit

P07

P06

P05

P04

P03

P02

P01

P00