1 overview of i/o ports, Overview of i/o ports, Functions of i/o ports – FUJITSU F2MC-8L F202RA User Manual

Page 92

76

CHAPTER 4 I/O PORTS

4.1

Overview of I/O Ports

Six I/O ports (comprising 26 pins) are available as general-purpose I/O ports (parallel I/O

ports).

These ports also serve peripherals (as I/O pins for specific peripheral functions).

■

Functions of I/O Ports

The I/O ports function to output data from the CPU to I/O pins via their port data register (PDR) and send

signals input to I/O pins to the CPU. For some ports, the I/O direction of I/O pins can be set by optionally

setting the bits of the port data direction register (DDR), with the bits corresponding to the pins.

The functions of the ports and peripherals for which the ports may serve are summarized below.

•

Port 0: General-purpose I/O port may also serve peripherals (external interrupt 2 and analog input pins)

•

Port 3: General-purpose I/O port may also serve peripherals (12-bit PPG, external interrupt 1, UART, 8-

bit serial I/O, 8/16-bit timers, and buzzer output pin)

•

Port 4: General-purpose I/O port of a type switched between CMOS push-pull and N-ch open-drain may

also serve peripherals (analog input pins)

•

Port 5: General-purpose I/O port may also serve peripherals (8-bit PWM pin)

•

Port 6: General-purpose I/O port (for MB89F202/F202RA, P61, P60 are input port)

•

Port 7: General-purpose I/O port

Table 4.1-1 lists the functions of the ports, and Table 4.1-2 lists the register of ports.

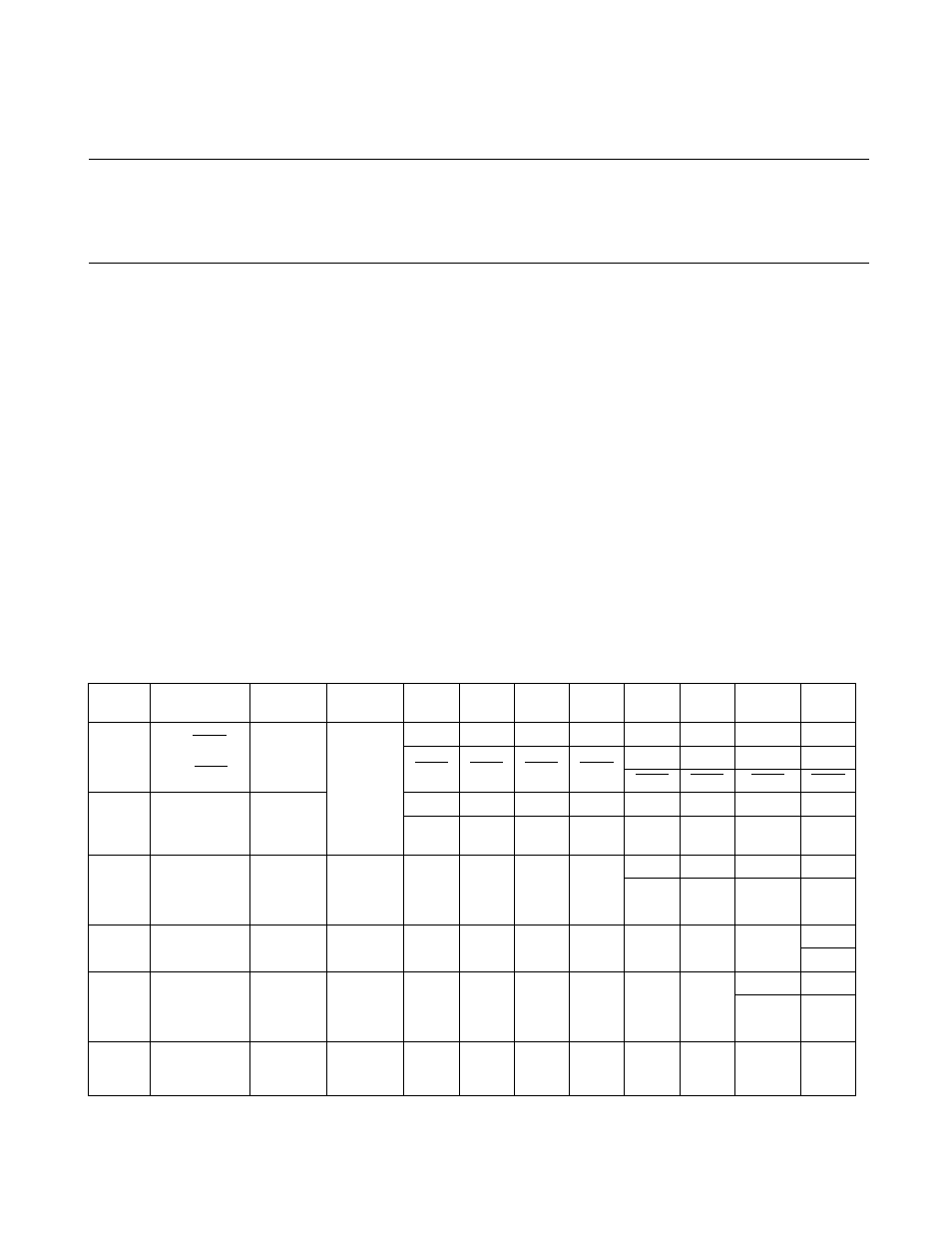

Table 4.1-1 Functions of Ports

Port

name

Pin name

Input

form

Output

form

bit7

bit6

bit5

bit4

bit3

bit2

bit1

bit0

Port 0

P00/INT20/

AN4 to

P07/INT27

Hysteresis

CMOS

analog

CMOS

push-pull

P07

P06

P05

P04

P03

P02

P01

P00

INT27

INT26

INT25

INT24

AN7

AN6

AN5

AN4

INT23

INT22

INT21

INT20

Port 3

P30/UCK/SCK

to

P37/BZ/PPG

CMOS

hysteresis

P37

P36

P35

P34

P33

P32

P31

P30

BZ/

PPG

INT12

INT11

TO/

INT10

EC

UI/SI

UO/SO

UCK/

SCK

Port 4

P40/AN0

to

P43/AN3

CMOS

analog

CMOS

push-pull

or N-ch

open-drain

-

-

-

-

P43

P42

P41

P40

AN3

AN2

AN1

AN0

Port 5

P50/PWM

CMOS

hysteresis

CMOS

push-pull

-

-

-

-

-

-

-

P50

PWM

Port 6

P60,

P61

CMOS

hysteresis

CMOS

push-pull

or N-ch

open-drain

-

-

-

-

-

-

P61

P60

-

-

Port 7

P70

to

P72

CMOS

CMOS

-

-

-

-

-

P72

P71

P70