FUJITSU F2MC-8L F202RA User Manual

Page 246

230

CHAPTER 10 EXTERNAL INTERRUPT CIRCUIT 1 (EDGE)

■

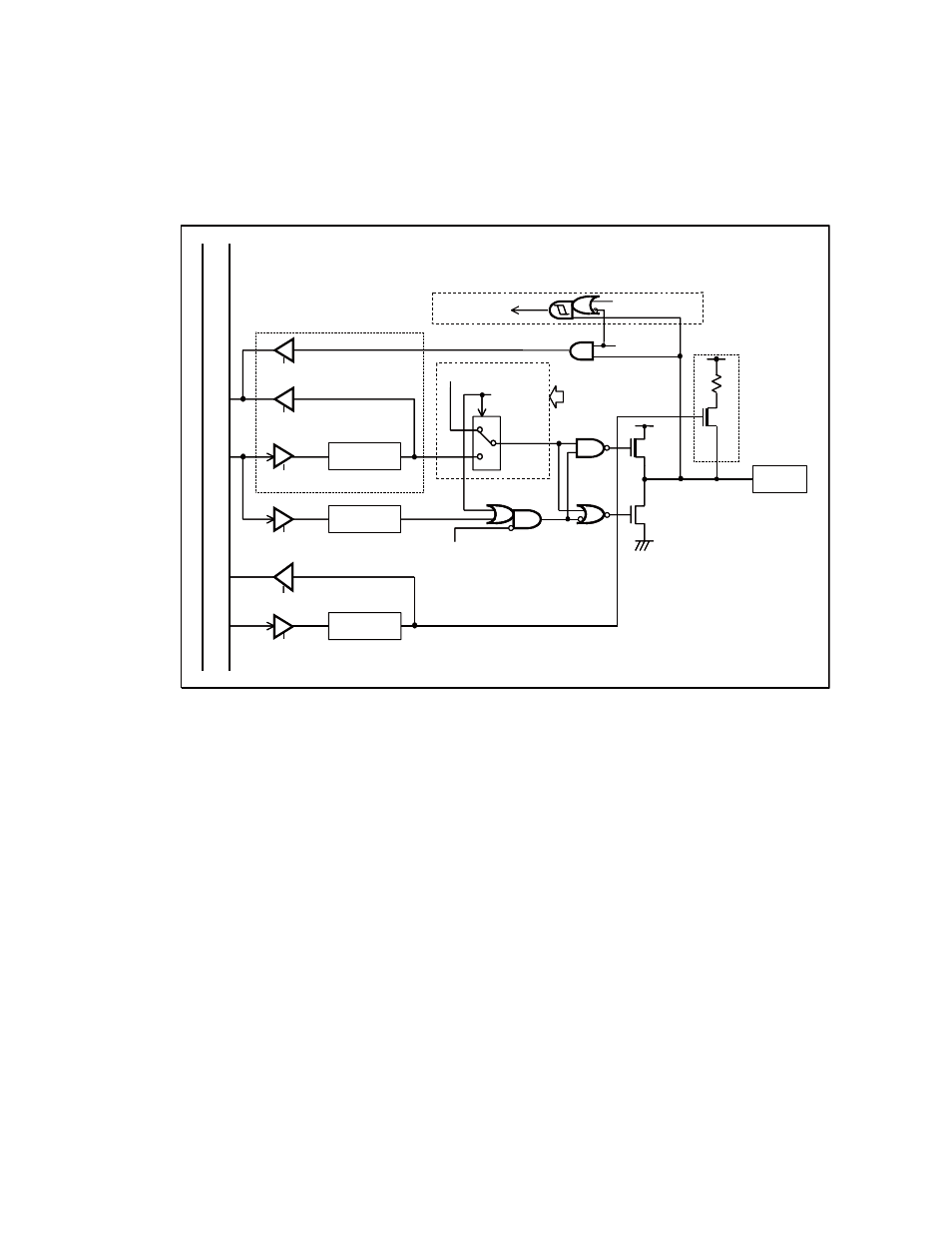

Block Diagram of Circuitry Terminating at the Pins Associated with External Interrupt

Circuit 1

Figure 10.3-1 Block Diagram of Circuitry Terminating at the Pins Associated with External Interrupt Circuit 1

Note:

When the ON setting of the pull-up resistor is selected by the pull-up setting register, the pin state will

be "H" level (pull-up state) rather than Hi-Z during stop mode (SPL = 1). During a reset, however, the

pull-up is invalid and the pin remains at Hi-Z.

DDR

N-ch

PDR

(SPL=1)

INT10,INT11

INT12

PUL

P34/TO/INT10

P35/INT11

P36/INT12

P-ch

PDR

P34/TO/INT10

P35/INT11

P36/INT12

Inter

nal data b

u

s

PDR read

PDR read

(when read-modify-write is

performed)

Output

latch

PDR write

DDR write

PUL read

PUL write

Stop mode (SPL=1)

Stop mode

Output from

peripheral Output

from

peripheral

enable

Output occurring

from peripheral

External interrupt

enable

Pull-up

resistor

Pins